# DALLAS JUXIJU

## DS2120 Ultra3 LVD SCSI Terminator

#### www.maxim-ic.com

#### FEATURES

- Fully Compliant with Ultra3, Ultra160, Ultra320, and Ultra2 (LVD only) SCSI

- Provides Low-Voltage Differential (LVD) Termination for Nine Signal Line Pairs

- Zero Temperature Coefficient Termination Resistors

- Autoselection of LVD Termination

- 5% Tolerance on LVD Termination Resistance

- Low Power-Down Capacitance of 3pF

- Built-In Mode Change Filter/Delay

- On-Board Thermal Shutdown Circuitry

- SCSI Bus Hot Plug Compatible

#### **APPLICATIONS**

Raid Systems SCSI Host Bus Adapter Cards (HBA) Servers SCSI Cables Network Attached Storage (NAS) Storage Area Networks (SANs)

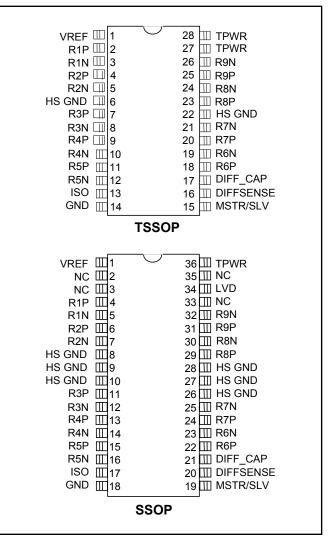

### **PIN CONFIGURATION**

#### **ORDERING INFORMATION**

| PART        | TEMP RANGE                       | VOLTAGE<br>(V) | PIN-PACKAGE            | TOP MARK* |

|-------------|----------------------------------|----------------|------------------------|-----------|

| DS2120B     | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 36 SSOP                | DS2120    |

| DS2120B/T&R | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 36 SSOP/Tape and Reel  | DS2120    |

| DS2120E     | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 28 TSSOP               | DS2120    |

| DS2120E+    | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 28 TSSOP               | DS2120    |

| DS2120E/T&R | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 28 TSSOP/Tape and Reel | DS2120    |

| DS2120E+T&R | $0^{\circ}$ C to $+70^{\circ}$ C | 5              | 28 TSSOP/Tape and Reel | DS2120    |

+ Denotes lead-free/RoHS-compliant package.

\* The top mark includes a "+" on lead-free packages.

## GENERAL DESCRIPTION

The DS2120 Ultra3 LVD SCSI terminator is a low-voltage differential (LVD) terminator. If the device is connected in an LVD-only bus, the DS2120 uses LVD termination. If any single-ended (SE) or high-voltage differential (HVD) devices are connected to the bus, the DS2120 disconnects from the bus. This is accomplished inside the part automatically by sensing the voltage on the SCSI bus DIFFSENS line.

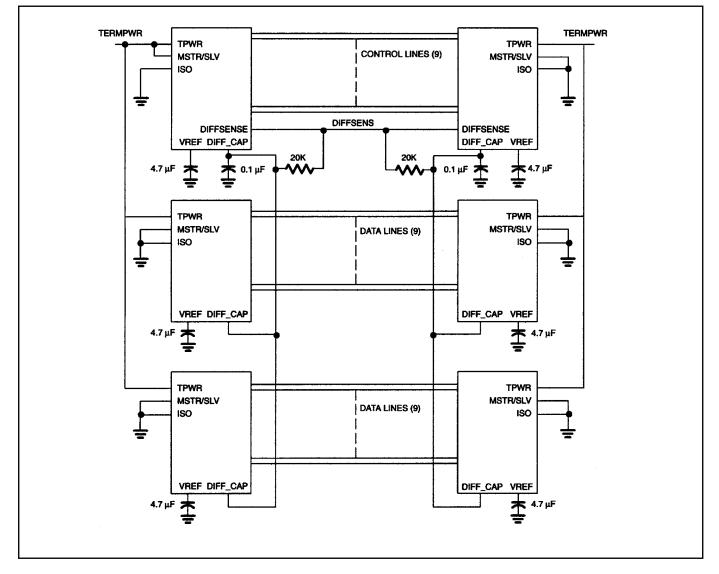

For the LVD termination, the DS2120 integrates two current sources with nine precision resistor strings. Three DS2120 terminators are needed for a wide SCSI bus.

#### **REFERENCE DOCUMENTS**

Small Computer Systems Interface (SCSI-3)SCSI Parallel Interface (SPI)Project: 0855-M, 1995Small Computer Systems Interface (SCSI-3)SCSI Parallel Interface 2 (SPI-2)Project: 1142-M, 1998Small Computer Systems Interface (SCSI-3)SCSI Parallel Interface 3 (SPI-3)Project: 1302-D, 1999Small Computer Systems Interface (SCSI-3)SCSI Parallel Interface 4 (SPI-4)Project: 1365-D, 200x

#### Available from:

American National Standards Institute (ANSI) Phone: 212-642-4900 Global Engineering Documents 15 Inverness Way East; Englewood, CO 80112 Phone: 800-854-7179

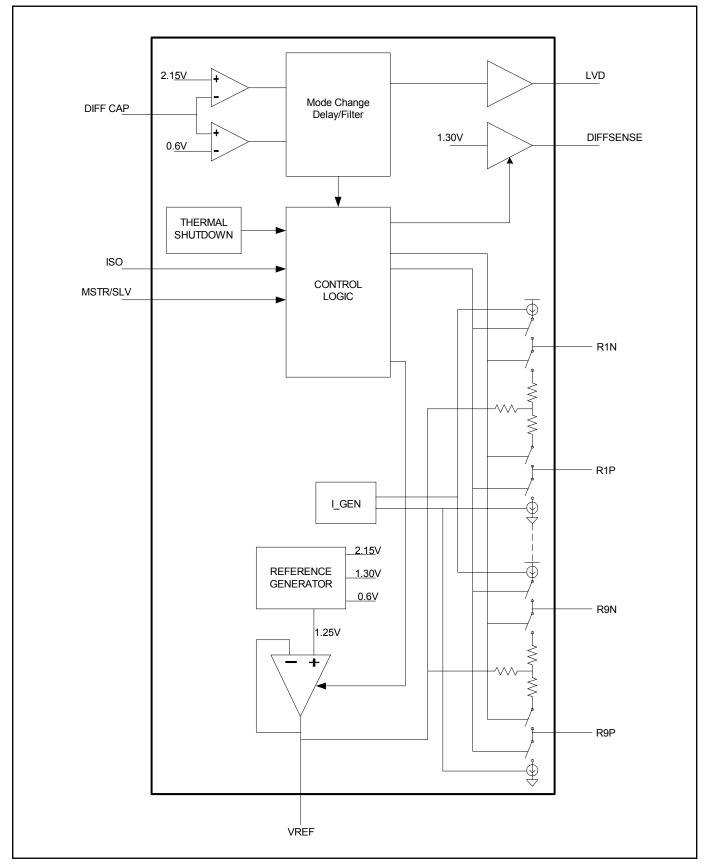

#### FUNCTIONAL DESCRIPTION

The DS2120 combines LVD termination with DIFFSENSE sourcing and detection.

LVD termination is provided by a laser-trimmed resistor biased with two current sources and a commonmode voltage source, generated from a bandgap reference of 1.25V. The configuration is a y-type terminator with a 105 $\Omega$  differential and 150 $\Omega$  common-mode resistance. A fail-safe bias of 112mV is maintained when no drivers are connected to the SCSI bus. In non-LVD mode, the resistors are isolated from the bus.

The DIFF\_CAP pin of DS2120 monitors the DIFFSENS line to determine the proper operating mode of the device. If the voltage on the DIFF\_CAP is between 0.7V and 1.9V, the device enters LVD mode after the mode-change delay. If the voltage at the DIFF\_CAP later crosses one of the thresholds, the DS2120 again changes modes after the mode-change delay. The mode-change delay is the same when changing in or out of LVD mode. A new mode change can start anytime after a previous mode change has been detected. These modes are the following:

- **LVD Mode:** LVD termination is provided by a precision laser-trimmed resistor string with two current sources. This configuration yields a  $105\Omega$  differential and  $150\Omega$  common-mode impedance. A fail-safe bias of 112mV is maintained when no drivers are connected to the SCSI bus.

- **SE Isolation Mode:** The DS2120 identifies that there is a SE (single-ended) device on the SCSI bus and isolates the termination pins from the bus.

- **HVD Isolation Mode:** The DS2120 identifies that there is an HVD device on the SCSI bus and isolates the termination pins from the bus.

When ISO is pulled high, the termination pins are isolated from the SCSI bus and VREF remains active. The mode-change delay/filter is still active and the LVD pin continues to indicate the correct bus mode.

During thermal shutdown, the termination pins are isolated from the SCSI bus and VREF becomes high impedance. The DIFFSENS driver is shut down during either of these two events. The DIFF\_CAP receiver is disabled and the LVD goes low, indicating a non-LVD condition.

To ensure proper operation, the TPWR pin should be connected to the SCSI bus TERMPWR line. As with all analog circuitry, the TERMPWR and  $V_{DD}$  lines should be bypassed locally. A 2.2µF capacitor and a 0.01µF high-frequency capacitor are recommended between TPWR and ground and placed as close as possible to the DS2120. The DS2120 should be placed as close as possible to the SCSI connector to minimize signal and power trace length, thereby lessening input capacitance and reflections that can degrade the bus signals.

To maintain the specified regulation, a  $4.7\mu$ F capacitor is required between the VREF pin and ground of each DS2120. A high-frequency cap ( $0.1\mu$ F ceramic recommended) can also be placed on the VREF pin in applications that use fast rise/fall-time drivers. A typical SCSI bus configuration is shown in Figure 2.

**DIFFSENS Noise Filtering:** The DS2120 incorporates a digital filter to remove high-frequency transients on the DIFFSENS control line, thereby eliminating erroneous switching between modes. This filter eliminates the need for the external capacitor and resistor, which previously performed this function. The external filter can be used in addition to the digital filter if the DS2120 and DS2118M or DS2119M are to be used interchangeably.

#### NOTES:

- 1) DIFFSENS: Refers to the SCSI bus signal.

- 2) DIFFSENSE: Refers to the Dallas Semiconductor pin name and internal circuitry relating to differential sensing.

### Figure 1. Block Diagram

Figure 2. SCSI Bus Configuration

#### **PIN DESCRIPTION**

| PIN                           |                                |           | EUNCTION                                                                                                                                                       |  |  |  |

|-------------------------------|--------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TSSOP                         | SSOP                           | NAME      | FUNCTION                                                                                                                                                       |  |  |  |

| 1                             | 1                              | VREF      | <b>Regulator Output Voltage.</b> 1.25V reference in LVD mode; must be decoupled with a 4.7µF cap.                                                              |  |  |  |

| 2-5, 7-12,<br>18-21,<br>23-26 | 4–7, 11–16,<br>22–25,<br>29–32 | RxP, RxN  | Signal Termination. Connect to SCSI bus signal lines.                                                                                                          |  |  |  |

| 6, 22                         | 8–10, 26–28                    | HS_GND    | <b>Heat Sink Ground.</b> Internally connected to the mounting pad. Should be connected to ground.                                                              |  |  |  |

| 13                            | 17                             | ISO       | <b>Isolation.</b> When pulled high, terminating resistors and biasing current sources are isolated from the SCSI bus.                                          |  |  |  |

| 14                            | 18                             | GND       | Signal Ground                                                                                                                                                  |  |  |  |

| 15                            | 19                             | MSTR/SLV  | <b>Master/Slave.</b> Mode select for the noncontrolling terminator. When pulled high (MSTR), the DIFFSENS driver is enabled.                                   |  |  |  |

| 16                            | 20                             | DIFFSENSE | <b>DIFFSENSE.</b> Output to drive the SCSI bus DIFFSENS line.                                                                                                  |  |  |  |

| 17                            | 21                             | DIFF_CAP  | <b>DIFFSENSE Capacitor.</b> Connect a 0.1µF capacitor for DIFFSENSE filter. Input to detect the type of device (differential or single-ended) on the SCSI bus. |  |  |  |

| 27, 28                        | 36                             | TPWR      | <b>Termination Power.</b> Connect to the SCSI TERMPWR line and decouple with 2.2µF capacitor.                                                                  |  |  |  |

|                               | 34                             | LVD       | <b>Low-Voltage Differential.</b> Output of DIFFSENSE receiver; output high indicates LVD bus operation.                                                        |  |  |  |

|                               | 2, 3, 33, 35                   | NC        | No Connection. Do not connect pins.                                                                                                                            |  |  |  |

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                   | SYMBOL                 | MIN  | TYP | MAX              | UNITS | NOTES |

|-----------------------------|------------------------|------|-----|------------------|-------|-------|

| Termpower Voltage, LVD Mode | V <sub>TPWR(LVD)</sub> | 2.7  |     | 5.5              | V     |       |

| Logic 0                     | $V_{IL}$               | -0.3 |     | +0.8             | V     | 13    |

| Logic 1                     | $V_{\mathrm{IH}}$      | 2.0  |     | $V_{TPWR} + 0.3$ | V     | 13    |

| Operating Temperature       | $V_{AMB}$              | 0    |     | 70               | °C    |       |

| PARAMETER               | SYMBOL           | MIN   | ТҮР  | MAX   | UNITS | NOTES |  |  |

|-------------------------|------------------|-------|------|-------|-------|-------|--|--|

| Differential Mode       | D                | 100   |      | 110   | Ω     |       |  |  |

| Termination Resistance  | R <sub>DM</sub>  | 100   |      | 110   | 52    |       |  |  |

| Common Mode Termination | D                | 110   |      | 190   | Ω     |       |  |  |

| Resistance              | R <sub>CM</sub>  | 110   |      | 190   | 52    |       |  |  |

| Differential Mode Bias  | V <sub>DM</sub>  | 100   |      | 125   | mV    | 2     |  |  |

| Common Mode Bias        | V <sub>CM</sub>  | 1.125 |      | 1.375 | V     |       |  |  |

| Output Capacitance      | C <sub>OUT</sub> |       |      | 3     | pF    | 1     |  |  |

| Mode-Change Delay       | M <sub>CD</sub>  | 0.66  | 1.25 | 2     | ms    | 1, 12 |  |  |

### LOW-VOLTAGE DIFFERENTIAL CHARACTERISTICS

## **DC CHARACTERISTICS**

| PARAMETER              | SYMBOL               | MIN  | ТҮР | MAX  | UNITS | NOTES     |

|------------------------|----------------------|------|-----|------|-------|-----------|

| Termpower Current      | I <sub>TPMR</sub>    |      | 12  | 30   | mA    | 2, 3      |

| Input Leakage High     | I <sub>IH</sub>      | -1.0 |     |      | μA    | 14, 15    |

| Input Leakage Low      | I <sub>IL</sub>      |      |     | 1.0  | μA    | 14, 15    |

| Output Current High    | I <sub>OH</sub>      |      |     | -1.0 | mA    | 4,6       |

| Output Current Low     | I <sub>OL</sub>      | 4.0  |     |      | mA    | 5,6       |

| DIFF_CAP LVD           | V <sub>LVDOR</sub>   | 0.7  |     | 1.9  | V     |           |

| Operating Range        | V LVDOR              | 0.7  |     | 1.9  | v     |           |

| DIFFSENSE Driver       | V <sub>DSO</sub>     | 1.2  |     | 1.4  | V     | 7, 8      |

| Output Voltage         | V DSO                | 1.2  |     | 1.4  | v     | 7, 0      |

| DIFFSENSE Driver       | I                    | 5    |     | 15   | mA    | 7, 9, 11  |

| Source Current         | I <sub>DSH</sub>     | 5    |     | 13   | IIIA  | 7, 9, 11  |

| DIFFSENSE Driver       | I                    | 20   |     | 200  | ۸     | 7, 10, 11 |

| Sink Current           | I <sub>DSL</sub>     | 20   |     | 200  | μA    | 7, 10, 11 |

| MSTR/SLV Input Leakage | I <sub>MSTRSLV</sub> | -6.5 |     | +125 | μA    |           |

| ISO Input Leakage      | I <sub>ISO</sub>     | -125 |     | +6.5 | μA    |           |

| Thermal Shutdown       |                      |      | 150 |      | °C    |           |

## **REGULATOR CHARACTERISTICS**

| PARAMETER            | SYMBOL            | MIN | ТҮР | MAX | UNITS | NOTES |

|----------------------|-------------------|-----|-----|-----|-------|-------|

| VREF Line Regulation | LI <sub>REG</sub> |     | 1.0 | 2.0 | %     |       |

| VREF Load Regulation | LO <sub>REG</sub> |     | 1.3 | 3.5 | %     |       |

| VREF Current Limit   | I <sub>LIM</sub>  |     |     | 200 | mA    |       |

| VREF Sink Current    | I <sub>SINK</sub> |     |     | 200 | mA    |       |

#### NOTES:

- 1) Guaranteed by design.

- 2) All lines open.

- 3) ISO = 1

- 4)  $V_{OUT} = 2.4V$

- 5)  $V_{OUT} = 0.4V$

- 6) LVD pin only.

- 7) MSTR/SLV = 1

- 8)  $I_{DS} = 0$  to 5mA

- 9)  $V_{\rm DSO} = 0.0 V$

- 10)  $V_{DSO} = 2.75 V$

- 11) TPWR = 5.5V

- 12)  $M_{CD}$  is extended by the RC time constant formed by the resistor connected from DIFFSENSE to DIFF\_CAP and the capacitor connected from DIFF\_CAP to ground.

- 13) MSTR/SLV and ISO pins.

- 14) Terminator pins only.

- 15) DIFFCAP pin only.

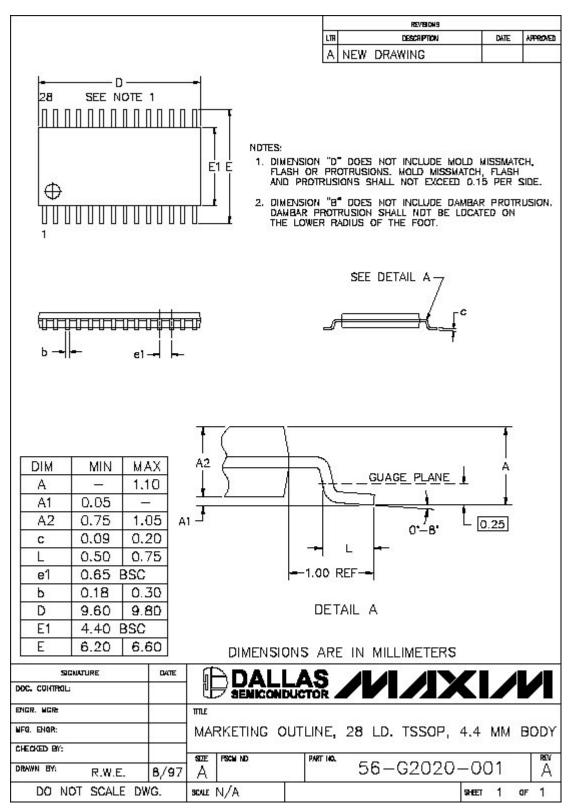

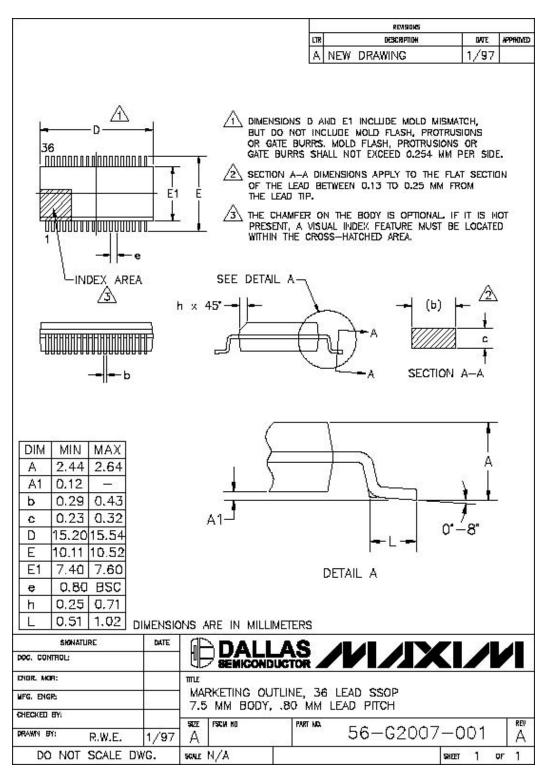

#### PACKAGE INFORMATION

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/DallasPackInfo</u>.)

#### PACKAGE INFORMATION (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <u>www.maxim-ic.com/DallasPackInfo</u>.)

#### 10 of 10

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

© 2006 Maxim Integrated Products • Printed USA

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.