Un ghid cuprinzător pentru protocolul de comunicare SPI

În acest articol, vom explora detaliile protocolului de interfață periferică serială (SPI), concentrându -ne pe capacitățile sale eficiente de transfer de date și aplicațiile versatile.SPI este un protocol de comunicare sincronă de mare viteză, utilizat pe scară largă în sistemele încorporate pentru a conecta microcontrolerele cu diverse periferice.Cu configurația sa master-sclave și patru linii de bază-MISO, MOSI, SCLK și CS-SPI simplifică comunicarea datelor, asigurând în același timp sincronizarea pe dispozitive.Vom săpa în principiile de bază ale SPI, inclusiv dinamica operațională, configurația hardware, diagramele de sincronizare și sfaturile de configurare practică.Indiferent dacă sunteți nou la SPI sau doriți să vă perfecționați înțelegerea, această postare va oferi informații valoroase pentru a maximiza potențialul său în aplicațiile reale.Catalog

Prezentare generală a protocolului SPI

Interfața periferică serială (SPI) utilizează un sistem cu 4 fire care eficientizează operațiunile CPU prin reducerea cheltuielilor software.Cunoscut pentru viteza și eficiența sa, SPI este de bază în dispozitive precum AT91RM9200.În cadrul maestrului-sclav, maestrul guvernează sarcinile prin interconectarea cu sclavii prin patru fire necesare: miso (Master in Slave Out), MOSI (Master Out Slave In), SCLK (ceas în serie) și CS (cip select).Linia MISO canalizează datele înapoi la Master, în timp ce MOSI gestionează datele de ieșire.SCLK oferă semnale de ceas de la master, iar CS facilitează controlul activării dispozitivului.Simplitatea SPI o face utilă în cea mai mare parte pentru conectarea mai multor dispozitive pe un singur autobuz, executarea transferului de date în serie și obținerea sincronizării prin impulsuri de ceas.Aici, maestrul poate întrerupe comunicarea fără a avea impact asupra fiabilității datelor.În timp ce SPI nu are caracteristici de control al fluxului și de recunoaștere a datelor, capacitatea sa de a mări conexiunile periferice prin decodificatoare externe compensează aceste limitări.

Cazuri specifice de utilizare SPI

SPI este construit în jurul unei configurații distinctive ale autobuzului cu inel folosind piese precum SS (CS), SCK, SDI și SDO pentru schimbul de date de înregistrare.Un transfer de înregistrare pe 8 biți, de exemplu, utilizează marginile ceasului pentru a gestiona mișcarea datelor și pentru a înregistra schimbările.Inițializarea într-o configurație master-sclave începe cu bufferele transceiver pre-configurare, ilustrând procesul de comunicare.SPI-ul Motorola excelează în comunicarea serială sincronă, folosind MOSI, MISO și SCK pentru sarcini avansate de primire, flexibilitate printre rolurile maestre-sclav și funcționalități robuste de ceas.Dispozitivele trebuie să sincronizeze faza de ceas și polaritatea pentru consecvența comunicării.Cu capacitatea de a conecta până la 256 de porturi, SPI se concentrează pe conectivitate punct-la-punct și transfer de date bazat pe pachete.

Formularea logică a utilizatorului

Proiectarea logicii utilizatorului adaptabile este dinamică pentru aplicațiile cu structuri cu mai multe porturi.În cadrul unei configurații cu dual-port, FIFO-urile independente gestionează datele în raport cu adresele portului.Concomitent, logica arbitraj supraveghează trecerea datelor către interfața SPI4, care se adaptează datelor de control imediat ale fluxului și stărilor FIFO.

Dinamica operațională SPI

SPI este conceput pentru o comunicare de încredere, cu canale discrete pentru controlul datelor și fluxului în transmisie.Conectivitatea portului extinsă permite transferurile de date bazate pe pachete, asigurând validarea punct-la-punct prin adrese de pachete, lărgind astfel versatilitatea aplicației.

Studiul diagramelor de sincronizare a transferului de date

Interfețele SPI sunt caracterizate prin patru diagrame de sincronizare contingente pe setările CPOL și CPHA.CPOL definește starea inactivă pentru SCK, în timp ce CPHA desemnează marginea ceasului de eșantionare.Aceste configurații sunt active pentru asigurarea preciziei și sincronizării datelor.

Comunicare serială sincronă

Originar de Motorola, SPI reprezintă un autobuz în serie în patru fire, bidirecțional, conceput pentru comunicații sincrone rapide, care leagă microcontrolerele de periferice precum EEPROMS, RTC și convertoare A/D.Rețeaua SPI conectează cu abilitate periferice mixte, folosind protocoale care ocolesc mecanismele de adrese pentru schimburi directe, complete-duplex.Linii suplimentare, cum ar fi INT, ar putea îmbunătăți receptivitatea sistemului.

Complicații în configurația hardware

În ciuda competenței SPI în interfațarea cu diverse periferice, semnalele de activare individuale pentru fiecare dispozitiv au ca rezultat o complexitate în comparație cu sistemele mai simple precum I2C.Această complexitate este un aspect intrinsec al configurației hardware SPI, încorporând registre de schimb pentru transferuri de date pe 8 biți.În timpul funcționării, dispozitivele se schimbă în siguranță prin registre folosind marginea de cădere a ceasului.

Evaluarea capacității și practicilor

Utilizarea elementelor precum Spiclk, MOSI, MISO și NSS, rețelele SPI stabilesc roluri maestre-sclave bazate pe state PIN NSS.Susținând medii unice sau multi-master, protocolul se adaptează la controlul a până la 16 periferice.Deși îi lipsește metodele de control și de recunoaștere a fluxului, structura protocolului se adaptează eficient la configurații și comunicații de conexiuni diverse.

Ilustrații de configurare și sincronizare

Tranzacțiile de date SPI sunt reglementate prin reguli simple de sincronizare influențate de gestionarea SCK.De exemplu, un model de înregistrare precum 10101010 trimite date bit-by-bit prin schimbări bazate pe ceas, subliniind simplitatea operațională și dinamica tranziției de date pe autobuzul inelar.

Perspective extinse despre performanță

Sincronizarea corectă a fazei de ceas SPI și a polarității pe dispozitivele Master și Slave este utilizată pentru tranzacțiile de date în curs.Parametri precum CPOL și CPHA ar trebui să se alinieze între dispozitivele din sistemele legate de SPI pentru a menține armonia comunicării.

Sfaturi practice de configurare

Reglajele la configurațiile de ceas SPI trebuie să țină cont de cererile de ceas ale dispozitivului sclav pentru a asigura precizia datelor în timpul ciclurilor de transfer.Recunoașterea marginilor semnalului în timpul transferurilor de date este serioasă pentru a preveni neconcordanțele de interconectare.Manualele de produse detaliază frecvent setările necesare, subliniind impactul alinierii precise de toamnă asupra preciziei transmisiei.

Bazele comunicării SPI

În centrul său, interfața periferică serială (SPI) servește ca un protocol de comunicare serială sincronă, sincron, necesitând în prealabil aranjamente pentru interacțiune.Această caracteristică diferențiază SPI prin evidențierea inerent a schimburilor sincronizate.Un aspect notabil al SPI este dependența sa de un model de maestru-sclav, în care dispozitivul principal orchestrează controlul prin generarea semnalelor de ceas și inițierea sesiunilor de comunicare.În schimb, dispozitivele sclave rămân acut reglate la aceste semnale, pregătite să participe atunci când sunt chemate.

Mecanismul de colaborare între dispozitivele maestru și sclav din SPI este organizat meticulos.Maestrul deține responsabilitatea exclusivă pentru gestionarea ceasului, asigurând un ritm constant pentru schimburile de date.Această supraveghere simplifică sincronizarea, eliminând imprevizibilitatea adesea prezentă în sistemele asincrone.Prin stabilirea unei referințe de timp unificate, ambele dispozitive pot executa operațiuni cu precizie, o practică rafinată prin experiență vastă în aplicație.Natura ordonată a SPI oferă capacități eficiente de transfer de date, prezentând o alternativă simplă la protocoale mai complexe.

Cadrul SPI dezvăluie constrângeri particulare, în special în setări care subliniază ușurința plug-and-play.Natura inflexibilă a protocolului său înseamnă compatibilitatea trebuie să fie aranjată meticulos în avans.Dispozitive din cadrul unei funcții de configurare SPI sub autoritatea semnalelor de ceas și a acordurilor de protocol predeterminate.Deși acest lucru simplifică sincronizarea, necesită eforturi inițiale de configurare.Aplicarea pricepută a acestor principii a demonstrat potențialul de a atenua discrepanțele de comunicare.După cum s -a observat în evaluările sesiunii, o înțelegere a rigurozității structurale a SPI nu numai că îmbunătățește implementarea practică, dar crește și precizia aplicației.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

Totul despre UDP: un ghid pentru comunicarea fără conexiune

pe 2024/12/30

Tehnologia HD: îmbunătățirea excelenței vizuale

pe 2024/12/30

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147749

-

Pinut și caracteristici USB-C

pe 2000/04/18 111907

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111349

-

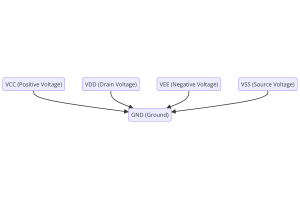

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83714

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79502

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66869

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63004

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 62945

-

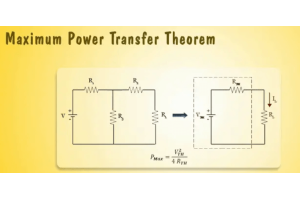

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54076

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52088