CPLD explicat: un ghid pentru dispozitivele logice programabile

În lumea dinamică a designului electronic, dispozitivele logice programabile complexe (CPLD) ies în evidență ca instrumente versatile, amestecând perfect adaptabilitatea, precizia și eficiența.Aceste dispozitive au revoluționat proiectarea circuitului prin introducerea celulelor macro programabile și o matrice interconectată dominantă, permițând crearea de funcții logice complexe cu o fiabilitate remarcabilă.De la înființarea lor în anii 1980 până la rolul lor cheie în industriile moderne precum rețelele, automobilele și aerospațiale, CPLD -urile s -au dovedit necesare pentru a căuta atât flexibilitate, cât și performanță.Acest articol sapă în călătoria CPLD -urilor, caracteristicile lor distincte, aplicațiile practice și metodologiile de programare care le fac o piatră de temelie în proiectarea logică digitală.Catalog

Prezentare generală a CPLD

În cadrul stăpânirii dispozitivelor logice programabile complexe (CPLD), se descoperă o tapiserie sofisticată a celulelor macro logice programabile, împletită printr -o matrice interconectată dominantă.Aceste linii de unități de celule macro (MC) și de intrare/ieșire (I/O) vă permit să proiectați în mod atenți circuitele, configurarea structurilor pentru funcții unice.Spre deosebire de dispozitivele care sunt perplexe de sincronizarea lor complexă de interconectare, CPLDS folosesc fire metalice imobile.Această caracteristică le conferă un comportament de ceas consecvent și previzibil, ceea ce face ca predicțiile de sincronizare să fie mai fiabile și mai precise.

Călătoria și utilizarea

Anii ’70 au prezentat apariția dispozitivelor logice programabile (PLD), încurajând o mișcare către unități macro programabile.Această schimbare a introdus o flexibilitate amplă a designului, diferențiați -le de circuitele digitale statice, deși utilitatea lor a fost inițial constrânsă la circuite mai simple.Apariția CPLD-urilor la mijlocul anilor '80 a revoluționat acest peisaj, deschizând calea pentru proiectele complexe ale circuitului.De atunci, s -au țesut în țesăturile industriilor precum rețelele, electronica auto, prelucrarea CNC și sistemele aerospațiale.Vă puteți aminti despre modul în care CPLDS a simplificat procesele care au cerut odată forță de muncă manuală minuțioasă, marcând un salt remarcabil în eficiență.

Calități distinctive ale CPLD -urilor

CPLD-urile se disting prin programarea lor adaptabilă, integrarea extinsă, capacitățile de dezvoltare rapidă și aplicabilitatea largă, împreună cu costurile de producție economice.Aceștia apelează la cei cu experiență hardware minimă, care servesc ca produse fiabile și sigure, care nu necesită teste exhaustive.Ca o dovadă a priceperii lor în proiectele de circuit pe scară largă, CPLD-urile joacă un rol cheie în dezvoltarea prototipurilor și servește sub 10.000 de unități, întruchipând o competență utilă pentru tine.Adeptatea cu care CPLD -urile se adaptează la cerințele proiectului în evoluție le câștigă adesea apreciere, subliniind versatilitatea lor reală în medii dinamice.

Metode de aplicare

Aceste circuite integrate vă permit să elaborați funcțiile logice adaptate nevoilor lor folosind atât scheme, cât și limbile de descriere hardware pe platformele de dezvoltare.De exemplu, în proiectarea unui robot telefonic, scheme și descrieri hardware sunt pregătite și compilate pe un computer.Folosind un cablu de descărcare, codul este transferat la CPLD pentru programarea în sistem, care cuprinde testarea, depanarea și îmbunătățirea proiectelor.Modelele realizate cu succes sunt apoi produse în masă prin replicarea jetoanelor CPLD.În proiecte precum sistemele de semafor, repetarea procesului de proiectare devine necesară, similar cu reconstrucția unei case pentru a -și restabili noutatea.Această metodologie repetitivă pune adesea temeiul pentru stăpânire, stimulând atât abilitățile, cât și încrederea.

Variante de frunte

De -a lungul anilor, companii precum Altera, Lattice și Xilinx au dezvăluit linii proeminente de CPLD -uri.Exemple de remarcat includ Altera EPM7128S, Lattice's LC4128V, și Xilinx XC95108 .Aceste modele au găsit roluri proeminente în diverse aplicații globale.Cei care au avut privilegiul de a lucra cu aceste produse distincte remarcă frecvent diferențele subtile, dar puternice, care optimizează funcționalități particulare.Aceasta reflectă un proces de selecție fină influențat de cerințele specifice ale proiectului, în care fiecare variantă deține apelul său unic.

Identificarea și clasificarea FPGA și CPLD

|

Aspect |

CPLD |

FPGA |

|

Formarea logică a comportamentului |

Formați un comportament logic folosind structura termenului de produs.

Exemple: Seria ISPLSI de zăbrele, seria XILINX XC9500, ALTERA MAX7000S

Seria, seria Mach Lattice |

Formați comportament logic folosind o metodă de căutare a tabelului.

Exemple: seria Xilinx Spartan, Altera Flex10K, Seria Acex1K |

|

Adecvare |

Potrivit pentru algoritmi și logică combinațională, lucrări

Mai bine cu declanșatoare limitate și termeni bogați de produs |

Potrivit pentru logica secvențială, funcționează mai bine cu

structuri bogate în declanșatori |

|

Întârziere de sincronizare |

Structura de cablare continuă asigură uniformă și

întârzieri de sincronizare previzibile |

Structura de cablare segmentată duce la o sincronizare imprevizibilă

întârzieri |

|

Flexibilitatea programării |

Circuitele interne fixe sunt modificate pentru programare.

Se utilizează o programare logică la nivel de bloc |

Cablajul intern este modificat pentru programare.Logică

Programarea la nivel de poartă permite o mai mare flexibilitate |

|

Integrare |

Integrare mai mică în comparație cu FPGA |

O integrare mai mare cu structura de cablare mai complexă și

Implementarea logică |

|

Ușurință de utilizare |

Mai ușor de utilizat cu programarea prin E2PROM sau FastFlash.

Nu este necesar un cip de memorie extern |

Necesită memorie externă pentru a stoca programarea

informații, ceea ce duce la o utilizare mai complexă |

|

Viteză și predictibilitate |

O viteză mai rapidă și o mai bună predictibilitate a timpului din cauza

interconectare umflată între blocurile logice |

Viteză mai lentă și sincronizare mai puțin previzibilă din cauza

programare la nivel de poartă și interconectare distribuită |

|

Tehnologia de programare |

Utilizează programarea E2PROM sau a memoriei flash.Date de programare

este păstrat atunci când sistemul este oprit.Acceptă programarea pe un

programator sau în sistem |

Bazat pe programarea SRAM.Datele de programare se pierd atunci când

Sistemul este oprit și trebuie reîncărcat.Suport dinamic

configurație |

|

Confidențialitate |

Oferă o mai bună confidențialitate |

Oferă confidențialitate mai mică |

|

Consumul de energie |

În general un consum de energie mai mare, în special cu

integrare mai mare |

Consum de energie mai mic în comparație cu CPLD |

Limbaj de programare a CPLD

Analizarea modului în care sunt programate dispozitivele logice programabile (CPLD) complexe este o piatră de temelie în elaborarea soluțiilor hardware versatile.Metodele istorice pentru programarea CPLD -urilor s -au bazat pe diagrame de scară sau pe limbajele de descriere hardware (HDL), Verilog HDL și VHDL fiind alegeri predominante.Limba selectată poate modela atât strategia de proiectare, cât și eficiența operațională a implementărilor.

• Verilog Hdl: Verilog HDL este prețuit pentru simpla sa sintaxă și capacități de simulare robuste, reflectând metodologiile utilizate în designul logic digital.Integrarea sa cu instrumentele de automatizare a proiectării electronice (EDA) vă permite să efectuați perfect sinteza și simularea.S-a observat că sintaxa asemănătoare cu C a Verilogului scade bariera de intrare pentru cei cu fundal de programare, grăbind călătoria de la proiectare la implementare pe o gamă largă de sectoare industriale.

• Vhdl: VHDL oferă o opțiune mai elaborată și mai expresivă pentru programarea HDL.Este frecvent alegerea pentru proiectele care necesită documentație minuțioasă și verificare riguroasă de tip, trăsături apreciate în industria aerospațială și de apărare.Puteți observa că, în ciuda complexității potențiale a VHDL în proiecte mai mici, structura sa disciplinată susține crearea de proiecte excepțional de fiabile, o necesitate în mediile în care siguranța este dominantă.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

Tranzistoare NMOS: proiectare, operare și aplicații

pe 2024/12/29

Transformarea rapidă Fourier (FFT): revoluționarea procesării digitale a semnalului

pe 2024/12/29

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147764

-

Pinut și caracteristici USB-C

pe 2000/04/18 111987

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111351

-

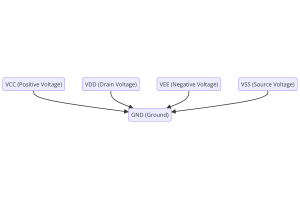

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83751

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79542

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66949

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63090

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63028

-

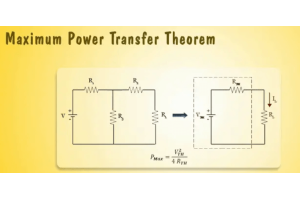

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54092

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52172