Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

Analizarea arhitecturii finale a procesatorilor de calculatoare dezvăluie complexitățile din spatele funcționării și performanței lor.Printre cele mai influente proiectări ale procesatorilor se numără computerul de instrucțiuni complexe (CISC) și arhitecturile reduse pentru setul de instrucțiuni (RISC).Fiecare oferă abordări unice pentru execuția instrucțiunilor, eficiența programării și designul hardware.Acest articol explorează complexitatea arhitecturii CISC, subliniind setul său de instrucțiuni extins care simplifică programarea în timp ce prezintă provocări hardware.De asemenea, săpă în abordarea RISC simplificată, care optimizează performanța printr -un set de instrucțiuni simplificat și eficient.În cele din urmă, postarea evidențiază modul în care procesoarele moderne adoptă din ce în ce mai mult arhitecturi hibride, amestecând punctele forte ale CISC și RISC pentru a răspunde nevoilor de calcul diverse.Catalog

Prezentare generală a CISC

Arhitectura unui procesor de calculator se concentrează în jurul executării unei game diverse de instrucțiuni sau microinstrucții, fiecare concepută pentru a îndeplini sarcini specifice.În timp ce un set de instrucțiuni mai cuprinzător poate face programarea pentru microprocesor mai intuitiv, poate introduce, de asemenea, obstacole potențiale de performanță.Arhitectura complexă a computerului de instrucțiuni (CISC) se remarcă datorită colectării sale vastă de instrucțiuni, inclusiv a celor complicate care simplifică experiența de programare în comparație cu arhitecturile alternative.Fiecare sarcină, simplă sau complexă, este asociată cu o instrucțiune unică, care reduce cantitatea de codificare necesară.Cu toate acestea, acest design complex poate reprezenta provocări notabile în dezvoltarea procesorului și a circuitelor unității de control asociate.

Arhitectura CISC se distinge printr -o selecție largă de microinstrucții care facilitează dezvoltarea programului pentru procesor.Aceste microinstrucții, adesea articulate în limbajul de asamblare, înlocuiesc anumite funcții care au fost gestionate în mod tradițional de software cu sisteme de instrucțiuni la nivel de hardware.Această schimbare nu numai că luminează volumul de muncă pentru dvs., dar permite și executarea simultană a operațiunilor de nivel scăzut în timpul fiecărui ciclu de instrucțiuni, sporind viteza generală a execuției computerului.

Frecvența utilizării instrucțiunilor în setul de instrucțiuni CISC prezintă un dezechilibru izbitor.Aproximativ 20% din instrucțiuni sunt utilizate în mod obișnuit, reprezentând aproximativ 80% din codul total al programului, în timp ce restul de 80% sunt rareori angajați, contribuind la doar 20% din programare.Această observație rezonează cu un principiu mai larg observat în diferite domenii: o mică selecție de instrumente sau metode produce adesea majoritatea rezultatelor.

Comparație CISC și RISC

Arhitectura setului de instrucțiuni reduse (RISC) se remarcă datorită setului său de instrucțiuni simplificat, care are ca scop creșterea eficienței procesorului.Totuși, acest design necesită o abordare mai sofisticată a programării externe.Concentrându -se pe cele mai utilizate instrucțiuni simple, RISC evită eficient complicațiile care însoțesc adesea comenzi mai complexe.

• Arhitectura RISC standardizează lungimea instrucțiunii.

• Simplifică formatele de instrucțiuni, bazându -se în principal pe logica de control.

• Această alegere de proiectare elimină necesitatea controlului microcodului, ceea ce duce la viteze operaționale mai rapide.

Originile RISC pot fi urmărite în cercetările inovatoare realizate de John Cocke la IBM.Descoperirile sale au indicat că doar aproximativ 20% din instrucțiunile computerului reprezintă aproximativ 80% din volumul de muncă de calcul.Această perspectivă are o greutate substanțială, ceea ce sugerează că, prin optimizarea instrucțiunilor cele mai frecvent executate, se pot obține îmbunătățiri extinse ale performanței.În consecință, sistemele RISC depășesc frecvent sistemele de informatică complexe de instrucțiuni complexe (CISC), alinându-se cu binecunoscutul principiu 80/20 care informează dezvoltarea arhitecturii RISC.

În timp ce RISC se mândrește cu mai multe avantaje, nu înlocuiește în întregime arhitectura CISC.Fiecare tip are punctele sale forte distincte, iar diferențele dintre ele au devenit mai puțin pronunțate în timp.În practica contemporană, multe procesoare moderne încorporează elemente atât din RISC, cât și din CISC, reflectând o tendință din ce în ce mai mare către arhitecturile hibride.De exemplu, procesoarele de instrucțiune ultra-lungi (ULIW) ilustrează acest amestec, îmbinând beneficiile ambelor arhitecturi pentru a produce o unitate de procesare mai adaptabilă.Această fuziune nu numai că sporește performanța, dar introduce și flexibilitate în programare, permițând o gamă mai largă de aplicații.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

Tehnologia Square Quad Flat Pachet (QFP): Proiectare, aplicații și provocări

pe 2024/12/30

Dispozitive logice programabile șters (EPLDS): un ghid pentru proiectare și aplicații

pe 2024/12/30

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147758

-

Pinut și caracteristici USB-C

pe 2000/04/18 111938

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111349

-

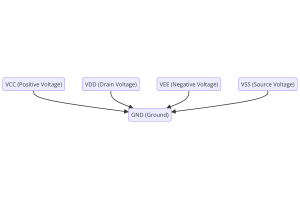

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83721

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79508

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66914

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63055

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63012

-

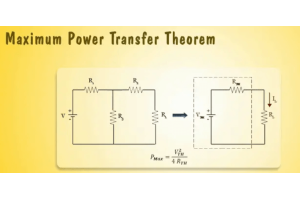

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54081

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52131