Ghid cuprinzător pentru bancile de testare: Instrumente și tehnici pentru verificarea sistemului digital

Acest ghid explorează testele de testare, un instrument cheie pentru validarea software -ului care simulează condițiile pentru a testa intrările și a verifica ieșirile.Testbenches joacă un rol în identificarea erorilor la începutul dezvoltării, îmbunătățind fiabilitatea software.Cu exemple și perspective practice, acest articol evidențiază utilizările, tehnicile și importanța lor în construirea de sisteme digitale puternice și eficiente.Catalog

Rolul testelor în validarea sistemului digital

Un banc de testare este o componentă în procesul de validare a sistemului digital.Nu este doar un instrument pentru generarea intrărilor și verificarea ieșirilor, ci servește ca un cadru cuprinzător care simulează condiții pentru a evalua fiabilitatea, funcționalitatea și comportamentul sistemelor digitale înainte de a fi implementate în domeniu.Prin crearea de medii controlate la sistemele de testare a stresului, cu o gamă largă de scenarii de intrare, testele de testare vă ajută să identificați defectele potențiale de proiectare la începutul ciclului de viață de dezvoltare, cu mult înainte ca sistemul să fie introdus în producție.Această detectare timpurie a erorilor și a vulnerabilităților este necesară pentru reducerea erorilor costisitoare, pentru a asigura respectarea specificațiilor de performanță și pentru a îmbunătăți fiabilitatea generală a sistemului.

În plus față de verificarea corectitudinii răspunsurilor sistemului, testele de testare joacă un rol în evaluarea cazurilor de margine, a problemelor de sincronizare și a mecanismelor de gestionare a erorilor, asigurându-se că sistemul poate funcționa corect chiar și în condiții extreme sau neașteptate.Prin testarea și simularea automată, bancile de testare contribuie la o calitate mai ridicată a software -ului, la performanțe îmbunătățite și la cicluri de dezvoltare mai scurte, permițând testarea iterativă fără intervenție manuală.Ele servesc ca o protecție împotriva eșecurilor care ar putea apărea după implementare, asigurând robustetea și fiabilitatea sistemelor digitale.

Componente cheie ale unui banc de testare și funcțiile acestora

Pentru a înțelege mai bine modul în care funcționează Banches, este important să explorați componentele care le fac eficiente.Un banc de testare bine lucrat funcționează prin gestionarea a două sarcini de bază: generarea de intrări (stimuli) și verificarea ieșirilor.Să examinăm în detaliu fiecare componentă.

Generarea stimulului

Generarea stimulului implică crearea unui set de semnale de intrare care simulează condiții pentru a testa comportamentul unui sistem digital.Aceste intrări trebuie să fie atât precise, cât și realiste pentru a se asigura că sistemul este supus unei varietăți de scenarii pe care le -ar putea întâlni în practică.Luați în considerare un modul RAM de bază ca exemplu.Benzul de testare trebuie să furnizeze intrări specifice modulului și să observe ieșirile sale pentru a se asigura că se comportă așa cum se așteaptă.Intrările cheie pentru un modul RAM includ de obicei:

• CLK (ceas): conduce calendarul sistemului.

• ADDR (Adresa): Specifică ce locație de date să acceseze.

• WEN (scriere de scriere): controlează dacă datele sunt scrise în memorie.

• Date: informațiile reale sunt scrise în modul.

Rezultatul, cunoscut sub numele de DataOut, reprezintă rezultatul operațiunilor interne ale modulului.SCRIPTING cu atenție modul în care aceste intrări sunt livrate și monitorizează datea de date, puteți verifica dacă sistemul funcționează corect în diferite scenarii.Gândiți -vă la generarea de stimulare ca la crearea unui scenariu de testare într -un laborator.La fel cum oamenii de știință controlează cu atenție condițiile pentru a observa reacțiile chimice, proiectanții digitali creează contribuții precise pentru a observa cum răspunde un sistem.

Verificarea ieșirii

Verificarea ieșirii este procesul de verificare a faptului că rezultatele reale ale sistemului se potrivesc cu rezultatele așteptate.Acest pas este esențial în prinderea erorilor mai devreme înainte de a evolua în probleme mai mari.Alții folosesc verificarea ieșirii pentru a confirma că sistemul îndeplinește funcționalitatea prevăzută și funcționează constant în diferite condiții.Verificarea ieșirii implică atât verificări automate, cât și manuale.De exemplu:

• Instrumente de verificare automată: Instrumente precum ModelSim și Quartus permit testarea automată, unde ieșirile sistemului sunt comparate cu rezultatele așteptate.Acest lucru accelerează procesul de verificare și reduce eroarea.

• Verificarea manuală (opțională): Pentru scenarii mai complexe, pot fi necesare verificări manuale pentru a se asigura că sunt acoperite cazuri de margine specifice.

Instrumente și tehnici pentru implementarea testului de testare

Quartus: simulare vizuală de intrare/ieșire

Quartus oferă o interfață grafică care aranjează vizual intrările și observă ieșirile.Această metodă poate fi benefică pentru începători sau pentru sisteme care necesită o abordare vizuală mai practică.Prin permițând să interacționeze cu o simulare printr -un mediu grafic, Quartus ajută la demitificarea relației dintre intrări și ieșiri, ceea ce face mai ușor să înțeleagă cum se comportă un sistem digital în timp.Unul dintre punctele forte ale Quartus este că este ideal pentru începători.Interfața sa intuitivă, vizuală, oferă o modalitate simplă de a vedea modul în care intrările afectează ieșirile fără a fi nevoie de scripturi extinse sau de cunoștințe de programare.Feedback -ul pe care îl oferă ajută la înțelegerea mai ușor comportamentul circuitelor, ceea ce îl face un instrument util pentru cei noi pentru proiectarea sistemului digital.Cu toate acestea, Quartus are limitele sale.Configurarea simulărilor în Quartus poate consuma mult timp, în special pentru proiecte mai complexe.Instrumentul este mai puțin flexibil în comparație cu instrumentele de simulare bazate pe scripturi, care pot oferi mai multe opțiuni de personalizare și automatizare.Pentru a lucra la sisteme pe scară largă sau extrem de detaliată, această lipsă de flexibilitate poate reprezenta o provocare.

ModelSim: simulare bazată pe text folosind scripturi

ModelSim adoptă o abordare diferită a simulării prin prioritizarea intrării bazate pe text prin scripturi.Creați scenarii de testare folosind scripturi Verilog (.V) sau VHDL (.VHD), mai degrabă decât să aranjeze vizual intrări și ieșiri.Această metodă oferă mai multă precizie și control.În loc să vă bazați pe o interfață grafică, definiți modul în care sistemul trebuie testat prin scripturi detaliate, permițând o mai mare personalizare și automatizare în procesul de simulare.Unul dintre punctele forte ale Modelsim este flexibilitatea pe care o oferă.Folosind scripturi, aveți mai mult control asupra scenariilor de testare, permițându -le să creeze simulări complexe și precise.Odată ce un designer este familiarizat cu sintaxa și fluxul de lucru, configurarea simulărilor poate fi mult mai rapidă în comparație cu utilizarea instrumentelor grafice precum Quartus.Posibilitatea de a reutiliza și modifica scripturile se adaugă și eficienței sale, în special în proiecte mai mari.Cu toate acestea, abordarea bazată pe text a modelelor vine cu anumite limitări.Necesită o înțelegere solidă a sintaxei Verilog sau VHDL, care poate reprezenta o provocare pentru începătorii care nu sunt familiarizați cu limbile de descriere a hardware -ului.Drept urmare, ModelsISIS are o curbă de învățare mai accentuată în comparație cu mai multe instrumente de simulare vizuală.Utilizatorii noi pot fi dificil să înceapă, dar, cu practica, precizia și flexibilitatea oferite de scripturi pot deveni un atu valoros.

Teoria și practica de legătură în verificare

Test Banches servesc ca o punte între proiectări și aplicații teoretice prin simularea modului în care un sistem digital se va comporta în diferite condiții, inclusiv cazuri de margine și intrări neașteptate.În proiectarea digitală, este adesea dificil să prezicem modul în care un sistem va efectua în practică bazat exclusiv pe modelele teoretice.Test -Benches închid acest decalaj, permițându -vă să treceți dincolo de conceptele de proiectare abstractă și să evaluați comportamentul unui sistem într -un mediu controlat, simulat.Unul dintre avantajele cheie ale utilizării instrumentelor de simulare în testele de testare este feedback -ul instant pe care îl oferă în timpul depanului.Instrumente precum multisim sau modelesim oferă reprezentări vizuale ale comportamentului sistemului, care arată modul în care modificările intrării intrări ale ieșirilor în timp.Acest feedback vă permite să identificați mai repede problemele, să urmăriți erorile la cauza lor principală și să le ajustați design -urile în consecință.De exemplu, dacă un sistem nu îndeplinește constrângerile de sincronizare sau prezintă un comportament neașteptat în anumite secvențe de intrare, un banc de testare poate evidenția aceste defecte imediat, cu mult înainte ca sistemul să fie construit fizic.Prin identificarea problemelor la începutul ciclului de proiectare, bancurile de teste reduc nevoia de reelaborare costisitoare și prototipare fizică, eficientizarea procesului de verificare.Această validare în stadiu incipient ajută la asigurarea faptului că sistemele digitale sunt atât corecte, cât și rezistente la condiții, ceea ce le face mai fiabile și reducând riscul de eșec după implementare.În acest fel, TestBenches acționează ca un instrument practic pentru transformarea proiectelor teoretice în robuste.

Arhitectura avansată a bancului de testare

Băncile de teste avansate depășesc testarea simplă de intrare-ieșire prin încorporarea componentelor suplimentare pentru a gestiona sisteme complexe.Un banc de testare standard include trei părți cheie: a Generator de stimul Pentru a crea semnale de intrare, a Proiectare în testare (DUT), care este hardware -ul testat și un Monitor de ieșire Aceasta verifică rezultatele preconizate.Aceste componente lucrează împreună pentru a asigura o verificare mai detaliată și mai precisă a proiectelor digitale.

Îmbunătățirea preciziei testbench -ului implică utilizarea tehnicilor care să asigure că un proiect se desfășoară în mod fiabil în diferite scenarii. Testare randomizată Introduce modele de intrare imprevizibile pentru a verifica stabilitatea sistemului în diferite condiții. Testarea cazurilor de margine Se concentrează pe situații de graniță în care sistemul este cel mai probabil să întâmpine erori.În sfârșit, Testarea regresiei Implică teste de re-rulare după modificări pentru a confirma că nu au fost introduse probleme noi, asigurându-se că sistemul rămâne consecvent și fără erori în timp.

SCRIPTING TESTURI

Pentru a crea bancuri de testare eficiente și fiabile în Verilog sau VHDL, urmați cele mai bune practici cheie.Începeți simplu, apoi extindeți -vă prin testarea funcționalității de bază mai întâi și adăugând treptat scenarii mai complexe.Utilizați comentarii și documentație pentru a vă face mai ușor scripturile de înțeles și întreținut, explicând clar fiecare secțiune.În cele din urmă, automatizați acolo unde este posibil pentru a economisi timp și a reduce erorile folosind bucle și funcții pentru a gestiona sarcini repetitive și modele de intrare.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

Buclă blocată în fază digitală (DPLL): proiectare, componente și operații

pe 2025/01/7

Evoluția și impactul arhitecturii RISC în calculul modern

pe 2025/01/7

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147758

-

Pinut și caracteristici USB-C

pe 2000/04/18 111958

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111349

-

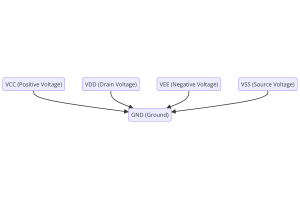

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83725

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79510

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66922

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63078

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63017

-

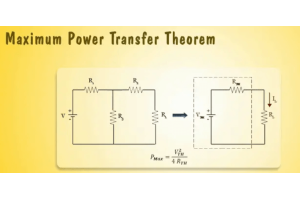

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54086

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52153