EP1C4F400C8 FPGA: Caracteristici, specificații, programare și alternative

Dacă lucrați cu logica programabilă, EP1C4F400C8 vă oferă un echilibru practic de performanță și costuri.În acest articol, veți afla care este acest FPGA, caracteristicile sale cheie, cum ar fi capacitatea logică, memoria și opțiunile de I/O și modul în care structura sa acceptă un design fiabil.Veți vedea, de asemenea, specificațiile sale, aplicațiile în sisteme, procesul de programare și modul în care se compară cu părțile similare.Catalog

Ce este EP1C4F400C8?

EP1C4F400C8 este membru al familiei FPGA a Intel (fosta Altera), concepută ca o soluție logică programabilă rentabilă și fiabilă.Construit pe un proces SRAM de 0,13 um, acest dispozitiv oferă o densitate logică moderată și opțiuni de I/O flexibile într-un pachet FBGA-400 compact.Familia Cyclone, care include dispozitive precum EP1C3, EP1C6, EP1C12 și EP1C20, a fost creată pentru a echilibra performanța și accesibilitatea pentru proiectele scalabile, permițând o migrare ușoară între nivelurile de densitate și pachete.Cunoscut pentru stabilitate și adopție largă, rămâne o alegere de încredere în proiectele moștenite.

Căutați EP1C4F400C8?Contactați -ne pentru a verifica stocul curent, timpul de plumb și prețurile.

Modele CAD EP1C4F400C8

Simbol EP1C4F400C8

Amprentă EP1C4F400C8

EP1C4F400C8 Model 3D

Caracteristici EP1C4F400C8

• Capacitate logică

EP1C4F400C8 oferă aproximativ 4.000 de elemente logice, organizate în 400 de blocuri logice (laboratoare).Acest lucru îl face potrivit pentru modele de gamă medie care necesită o densitate logică moderată, menținând în același timp eficiența costurilor.

• Memorie încorporată

Integrează aproximativ 76,5 kbits de memorie încorporată.Acest RAM intern acceptă funcții de tamponare, stocare și memorie mică, reducând nevoia componentelor de memorie externe în multe modele.

• Count I/O ridicat

Dispozitivul oferă 301 pini de I/O de consiliere utilizator în pachetul său FBGA cu 400 de bile.Acest număr ridicat de pini permite conectivitatea bogată pentru sisteme complexe care necesită mai multe interfețe periferice.

• Standarde I/O largi

Suporta mai multe standarde I/O, inclusiv LVTTL, LVCMOS, SSTL-2, SSTL-3 și LVD-uri diferențiale.Această flexibilitate permite FPGA să interfațăm direct cu o varietate de familii logice moderne și dispozitive de memorie.

• Semnalizare diferențială de mare viteză

Cu LVDS acceptă până la 640 Mbps, FPGA se ocupă de cerințele rapide de transfer de date.Acest lucru îl face practic pentru aplicații precum legături de comunicare de mare viteză și interfețe digitale rapide.

• Gestionarea ceasului cu PLL -uri

CIP integrează două bucle blocate în fază (PLL) și opt rețele de ceas global.Aceste caracteristici permit generarea precisă a ceasului, înmulțirea și controlul bruiajului pentru aplicații critice.

• Funcționare de bază de joasă tensiune

Funcționând la o tensiune de bază nominală de 1,5 V, dispozitivul echilibrează performanța cu un consum de energie mai mic.Acest nivel de tensiune a fost optimizat pentru tehnologia CMOS de 0,13 µm utilizată în fabricarea acesteia.

• Tensiuni I/O flexibile

FPGA acceptă tensiuni I/O de 1,5 V, 1,8 V, 2,5 V și 3,3 V pe diferite bănci.Această versatilitate îi permite să interfațăm atât cu componentele moștenitoare, cât și cu cele moderne ale sistemului.

• Configurare bazată pe SRAM

Ca și alte FPGA-uri cu cicloni, este bazat pe SRAM și necesită reconfigurare la fiecare power-up.Aceasta oferă flexibilitate pentru actualizări, dar necesită și un dispozitiv de configurare extern sau un controler.

• Suport de compresie bitstream

EP1C4F400C8 acceptă încărcarea bitstream comprimată în timpul configurației.Aceasta reduce cerințele de memorie externe și accelerează timpii de configurare.

• Conformitatea PCI

Include suport încorporat pentru standardele PCI (33/66 MHz, 32/64 biți).Această caracteristică permite ca dispozitivul să fie integrat direct în sisteme care necesită interfațare PCI fără o logică suplimentară de legătură.

Structura laboratorului ciclon

Diagrama arată structura logică a blocului (laborator) utilizat în FPGA -uri ciclonice precum EP1C4F400C8.Fiecare laborator se conectează la o rețea de interconectări: interconectări de rând, interconectări de coloane și interconectări locale, care se semnalează între elemente logice și alte blocuri.Interconectările de legătură directă oferă căi rapide, cu latență scăzută către laboratoarele adiacente, îmbunătățind performanța de sincronizare pe căile de semnal.Această arhitectură este importantă, deoarece echilibrează flexibilitatea de rutare cu eficiență, permițând FPGA să se ocupe de proiecte complexe, păstrând viteza și zona optimizată.

Ciclone I/O Diagrama băncilor

Diagrama ilustrează structura I/O Bank a FPGA -urilor ciclonice, cum ar fi EP1C4F400C8.Dispozitivul este împărțit în patru bănci I/O, fiecare alimentat de propriul său autobuz de aprovizionare, permițând să amestece diferite standarde de tensiune într -un singur FPGA.Toate băncile acceptă o gamă largă de standarde I/O, inclusiv LVTTL, LVCMOS, LVDS, RSDS și SSTL, în timp ce băncile 1 și 3 acceptă, de asemenea, PCI de 3,3 V pentru compatibilitate cu sisteme vechi.Această arhitectură I/O flexibilă este importantă, deoarece permite o integrare perfectă cu diverse dispozitive și interfețe externe, ceea ce face ca FPGA să fie adaptabil la diverse aplicații.

Specificații EP1C4F400C8

|

Tip |

Parametru |

|

Producător |

Alterra/Intel |

|

Serie |

Cyclone® |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Numărul de laboratoare/CLBS |

400 |

|

Numărul de elemente/celule logice |

4000 |

|

Biți de ram totale |

78.336 |

|

Numărul de I/O. |

301 |

|

Tensiune - alimentare |

1.425V ~ 1.575V |

|

Tip de montare |

Montare la suprafață |

|

Temperatura de funcționare |

0 ° C ~ 85 ° C (TJ) |

|

Pachet / carcasă |

400-BGA |

|

Pachet de dispozitive furnizor |

400-FBGA (21 × 21) |

|

Numărul produsului de bază |

EP1C4 |

Aplicații EP1C4F400C8

1. Procesarea digitală a semnalului (DSP)

EP1C4F400C8 poate fi programat pentru a efectua sarcini precum filtrarea, FFT și modularea semnalului.Combinația sa de elemente logice și memoria încorporată o face potrivită pentru procesarea de mare viteză.Acest lucru îi permite să înlocuiască cipurile DSP tradiționale cu o soluție FPGA flexibilă care poate fi reprogramată pentru diferiți algoritmi.

2. Sisteme încorporate și de control

În sistemele industriale și încorporate, acest FPGA este adesea utilizat pentru a implementa controlere personalizate, secvențiere și mașini de stat.Logica sa reconfigurabilă permite să adapteze comportamentul hardware exact la nevoile sistemului.Prin integrarea logicii de control în FPGA, numărul de componente externe este redus, îmbunătățind fiabilitatea și scăderea costurilor.

3. Comunicare și interfață de legătură

Dispozitivul acceptă mai multe standarde I/O și poate acționa ca o punte între diferite protocoale de comunicare.Este adesea folosit pentru a conecta PCI, LVD -urile, SDRAM și alte interfețe fără probleme în cadrul unui sistem.Acest lucru îl face foarte util în echipamentele de rețea, controlerele încorporate și conversii de interfață moștenită-modernă.

4. Achiziționarea și procesarea datelor

Cu disponibilitate ridicată I/O și memorie flexibilă, EP1C4F400C8 este potrivit pentru sistemele de colectare a datelor.Poate interfața direct cu ADC -urile și senzorii, poate prelucra datele în timp și le poate pregăti pentru stocare sau transmisie.Astfel de aplicații sunt frecvente în instrumente medicale, echipamente de testare și dispozitive de măsurare științifică.

EP1C4F400C8 Piese similare

|

Specificații |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Producător |

Alterra (Intel) |

Alterra (Intel) |

Alterra (Intel) |

Alterra (Intel) |

Alterra (Intel) |

Alterra (Intel) |

|

Familia FPGA |

Ciclon (EP1C4) |

Ciclon (EP1C4) |

Ciclon (EP1C4) |

Ciclon (EP1C4) |

Ciclon (EP1C4) |

Ciclon (EP1C4) |

|

Elemente logice (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Memorie încorporată (biți) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

Pinii I/O. |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pachet / carcasă |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Grad de viteză |

C8 |

C8 |

C8 |

C6 (mai rapid) |

C8 |

C8 |

|

Tensiune de bază |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Temp de funcționare.Gamă |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 Etape de programare

Înainte de a putea utiliza EP1C4F400C8 FPGA, trebuie să încărcați designul în dispozitiv.Programarea implică configurarea FPGA cu un fișier bitstream, astfel încât să știe să se comporte ca circuit prevăzut.

1. Selectați schema de configurare și setați pinii MSEL

Începeți prin a alege schema de configurare care se potrivește cel mai bine configurației dvs., cum ar fi serialul activ, serialul pasiv sau JTAG.Acest lucru se face prin setarea pinilor MSEL la niveluri logice specifice înainte de pornire.Fiecare mod folosește pini și protocoale diferite, de aceea trebuie să confirmați compatibilitatea cu instrumentele de proiectare și memoria de configurare.A face alegerea corectă aici asigură un proces de configurare lină.

2. Aplicați puterea și inițializați dispozitivul

În continuare, alimentați cu șinele de bază și I/O ale FPGA în intervalele de tensiune specificate.În timpul pornirii, mențineți pinul nconfig scăzut pentru a menține dispozitivul în resetare până când tensiunile de alimentare sunt stabile.Odată stabil, eliberați resetarea și dispozitivul semnalează pregătirea conducând pinul NSTATUS.Acest lucru garantează că FPGA este inițializat corespunzător înainte de începerea configurației.

3. Transmiteți bitstream -ul de configurare

În această etapă, trimiteți fișierul de date de configurare (bitstream) în FPGA folosind schema selectată.În modul serial sau pasiv activ, bitstream -ul provine de la un dispozitiv de memorie externă, în timp ce JTAG permite programarea directă prin cablu.Dispozitivul citește continuu în datele de configurare până la finalizare.Software -ul dvs. de proiectare generează acest bitstream pentru a se potrivi cu cerințele logice.

4. Confirmați configurația de succes (conf_done)

Când FPGA se termină încărcarea, acesta afirmă pinul Conf_done pentru a arăta că datele de configurare au fost primite cu succes.În același timp, dispozitivul efectuează inițializarea internă, cum ar fi compensarea registrelor și activarea I/O.Dacă conf_done nu reușește să ajungă la mare, înseamnă de obicei că datele de configurare sau configurarea au o eroare.Vizionarea acestui pin este cea mai simplă modalitate de a verifica procesul complet.

5. Efectuați o reconfigurare opțională în sistem

În cele din urmă, aveți opțiunea de a actualiza sau reprograma FPGA fără a -l scoate din bord.Folosind JTAG sau un controler încorporat, puteți încărca direct un nou bitstream, ceea ce este util pentru actualizările firmware -ului.Această flexibilitate vă permite să modificați, să depanați sau să actualizați sistemul dvs. chiar și după implementare.Se asigură că designul dvs. bazat pe FPGA se poate adapta în timp la schimbarea cerințelor.

EP1C4F400C8 Avantaje și dezavantaje

Avantaje

• Alegerea rentabilă pentru proiectele de gamă medie

• Numărul ridicat de I/O în comparație cu dispozitivele de densitate similare

• Tensiune flexibilă și suport standard I/O

• Susținut de instrumente și documentație matură

• Utilizare mai mică a puterii decât generațiile FPGA mai vechi

Dezavantaje

• învechit cu o disponibilitate limitată pe termen lung

• Logică mai mică și capacitate de memorie față de FPGA modernă

• Viteza de funcționare mai lentă și performanța I/O

• Necesită memorie externă pentru configurare la pornire

• Lipsește funcții avansate, cum ar fi blocurile DSP și transceiver-urile de mare viteză

EP1C4F400C8 Dimensiuni de ambalare

|

Tip |

Parametru |

|

Tip de pachet |

FBGA (tablou de grilă cu bilă fină) |

|

Număr de mingi |

400 |

|

Ball Pitch (E) |

1,0 mm (tipic pentru ciclon EP1C4F400) |

|

Diametrul bilei (B) |

0,45 mm (nominal) |

|

Dimensiunea pachetului (D × E) |

21 mm × 21 mm |

|

Înălțimea pachetului (a) |

2,40 mm (max) |

|

Grosimea substratului (A2) |

~ 0,40 mm |

|

Grosimea capacului de mucegai (A3) |

~ 1,90 mm |

|

Înălțimea mingii (A1) |

0,25 mm (nominal) |

|

Pin A1 colț |

Marcat pentru orientare |

|

Aspect de matrice |

20 × 20 grilă (cu bile de colț care lipsesc) |

|

Montare |

Montare la suprafață (SMD) |

EP1C4F400C8 Producător

EP1C4F400C8 a fost fabricat inițial de Altera Corporation, un pionier în dispozitivele logice programabile și tehnologia FPGA.În 2015, Altera a fost achiziționată de Intel Corporation, iar linia de produse a devenit parte a grupului de soluții programabile Intel (PSG).Astăzi, Intel susține aceste dispozitive Moștenite Altera, concentrându -se în același timp dezvoltarea pe familii FPGA mai noi, asigurând continuitatea utilizatorilor existenți și avansează inovația în logica programabilă.

Concluzie

EP1C4F400C8 se remarcă ca un FPGA eficient și versatil, care oferă performanțe solide pentru modele de gamă medie.Cu cele 4.000 de elemente logice, memoria încorporată, suportul I/O extins și compatibilitatea cu mai multe standarde de tensiune și interfață, oferă flexibilitate în aplicații variate.Arhitectura sa, procesul de programare și utilizarea largă în DSP, sistemele încorporate și achiziția de date îl fac o alegere practică, în ciuda statutului său moștenitor.În timp ce îi lipsește caracteristici avansate găsite pe dispozitive mai noi și se confruntă cu o disponibilitate limitată pe termen lung, rămâne o opțiune fiabilă care caută soluții dovedite în proiectele FPGA scalabile.

Fișă de date pdf

Fisa de date EP1C4F400C8:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Ce instrumente sunt necesare pentru a programa EP1C4F400C8?

Aveți nevoie de software-ul Quartus Intel (anterior Altera Quartus II) împreună cu un cablu de programare acceptat, cum ar fi USB-Blaster.Aceste instrumente vă permit să creați bitstream -ul și să îl încărcați în FPGA.

2.. EP1C4F400C8 poate gestiona direct aplicațiile PCI?

Da, are o conformitate încorporată pentru standardele PCI (33/66 MHz, 32/64-bit), ceea ce îl face potrivit pentru integrarea sistemului bazat pe PCI, fără a necesita o logică suplimentară de legătură.

3. Ce se întâmplă dacă EP1C4F400C8 nu reușește în timpul configurației?

Dacă configurația eșuează, PIN -ul Conf_done nu va afirma mare.Acest lucru indică de obicei o eroare în fișierul bitstream, secvențarea tensiunii sau configurarea pinului și ar trebui verificată în fluxul de proiectare.

4. poate interfața EP1C4F400C8 direct cu memoria DDR?

Suportă mai multe standarde I/O, dar nu are interfețe DDR native precum FPGA modernă.Pot fi necesare considerente suplimentare de proiectare sau componente de legătură.

5. Cum se compară EP1C4F400C8 cu FPGA mai nou?

În comparație cu dispozitivele moderne, EP1C4F400C8 are o viteză mai mică, o densitate logică mai mică și mai puține caracteristici avansate.Cu toate acestea, rămâne o alegere rentabilă pentru modele stabile și de gamă medie, unde nu este necesară performanțele de ultimă oră.

EPM3256AFC256-7 Prezentare generală a CPLD: Caracteristici, Pinout, Programare și Aplicații

pe 2025/10/3

ADG432BR Switch analog IC: Specificații, PINOUT, alternative și fișă de date

pe 2025/10/2

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147780

-

Pinut și caracteristici USB-C

pe 2000/04/18 112042

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111352

-

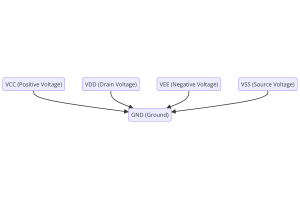

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83806

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79605

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66983

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63113

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63048

-

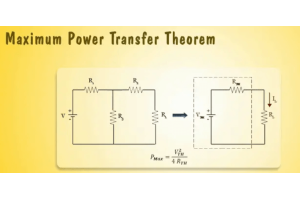

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54097

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52199