EPM7064STC100-7 CPLD: Caracteristici, aplicații și Ghid de programare în sistem

EPM7064STC100-7 este un cip puternic din seria Intel Max® 7000S, concepută pentru a gestiona sarcini complexe în dispozitivele electronice.Acest ghid discută principalele caracteristici și utilizări ale EPM7064STC100-7, subliniind capacitatea sa de a fi reprogramat cu ușurință, funcționarea rapidă și designul său flexibil.Ideal pentru multe tehnologii diferite, de la gadgeturi mici la mașini industriale mari, acest cip este o piesă cheie pentru construirea circuitelor digitale avansate.Catalog

EPM7064STC100-7 Descriere

EPM7064STC100-7 este un dispozitiv logic programabil complex (CPLD) din seria Intel Max® 7000S.Are 64 de macroceluri și 1.250 de porți, care ajută la construirea circuitelor digitale complexe.Acest cip rulează cu o viteză maximă de 166,7 MHz, cu o întârziere a semnalului de 7,5 nanosecunde (NS).Are 68 de pini de intrare/ieșire (I/O) care funcționează cu logică de 3.3V și 5V, ceea ce face ușor de utilizat în diferite circuite.O caracteristică cheie este programabilitatea sa de 5.0V în sistem (ISP) printr-o interfață JTAG (IEEE 1149.1).Acest lucru înseamnă că îl puteți reprograma fără a -l scoate din circuit, de a face testarea și actualizările mai ușor.Acesta vine într-un pachet plat subțire de 100 de pini (TQFP), care este un pachet compact, montat la suprafață.Acest CPLD este utilizat în sisteme încorporate, procesare digitală a semnalului, dispozitive de comunicare și automatizare industrială.

Oferim componente de înaltă calitate și servicii personalizate, așa că cel mai bine este să plasați comanda dvs. în vrac cu noi pentru soluții CPLD fiabile.

Caracteristici EPM7064STC100-7

• Logică de înaltă densitate: EPM7064STC100-7 este proiectat cu 64 de macroceluri și 1.250 de porți utilizabile, ceea ce îl face extrem de potrivit pentru implementarea funcțiilor logice complexe în circuitele digitale.Această arhitectură de înaltă densitate permite crearea de modele logice complexe, menținând în același timp eficiența în operațiunile logice programabile.Structura macrocell bine optimizată asigură utilizarea eficientă a resurselor disponibile, susținând implementări logice combinaționale și secvențiale avansate.

• Performanță rapidă: Construită pentru procesare de mare viteză, EPM7064STC100-7 funcționează cu o frecvență internă maximă de 166,7 MHz, permițând executarea rapidă a funcțiilor logice.Întârzierea de propagare de 7,5 ns asigură o latență minimă.Această capacitate de comutare rapidă îmbunătățește capacitatea dispozitivului de a gestiona eficient prelucrarea datelor de mare viteză, condiționarea semnalului și sarcinile de control, ceea ce îl face o alegere fiabilă pentru a solicita sisteme digitale.

• I/O versatil: Cu 68 de pini de intrare/ieșire programabile, EPM7064STC100-7 oferă o flexibilitate excepțională pentru integrarea în diverse proiecte de circuit.Susținând atât niveluri logice de 3.3V cât și 5V, permite o compatibilitate perfectă cu diferite tensiuni de sistem, eliminând necesitatea schimbătoarelor suplimentare de nivel de tensiune.Această adaptabilitate o face bine potrivită pentru aplicațiile din medii de tensiune mixtă, asigurând aplicabilitate largă pe sisteme încorporate, controale industriale și rețele de comunicații.

• Programmabilitate în sistem (ISP): Unul dintre avantajele EPM7064STC100-7 este programabilitatea sa de 5.0V în sistem (ISP), facilitată printr-un IEEE Std.1149.1 Interfață JTAG.Această caracteristică permite reprogramarea și modificarea funcțiilor logice fără a desolidenta sau a elimina fizic dispozitivul, simplificând întreținerea, depanarea și dezvoltarea iterativă.Capacitatea ISP reduce timpul de oprire și îmbunătățește flexibilitatea actualizărilor de firmware, ceea ce o face de neprețuit pentru proiectele digitale dinamice și reconfigurabile.

EPM7064STC100-7 Modele CAD

Simbol EPM7064STC100-7

EPM7064STC100-7 Amprentă

EPM7064STC100-7 Model 3D

EPM7064STC100-7 Diagrama blocului

EPM7064STC100-7 Diagrama blocului arată modul în care elementele logice ale cipului sunt conectate și controlate.Are patru blocuri logice (laboratoare), etichetate A, B, C și D, fiecare conținând 16 macroceluri.Aceste macroceluri îndeplinesc funcții logice și se conectează printr -un tablou de interconectare programabil (PIA), care permite rutarea flexibilă a semnalelor.Fiecare laborator este legat de un bloc de control I/O, gestionând până la 16 pini de intrare/ieșire pe laborator.Diagrama arată, de asemenea, semnale de control global (GCLK1, GCLK2, OE1 și GCLRN) care ajută la gestionarea funcțiilor de ceas și resetare pentru cip.Unele porți logice procesează aceste semnale înainte de a ajunge la diferite părți ale sistemului.Proiectarea EPM7064STC100-7 îi permite să fie utilizată în diverse aplicații logice programabile, cum ar fi mașini de stat, decodarea adreselor și alte circuite digitale personalizate.Interconectările sale flexibile asigură un flux de semnal eficient și o funcționare fiabilă.

Specificații EPM7064STC100-7

|

Tip |

Parametru |

|

Producător |

Alterra/Intel |

|

Serie |

Max® 7000s |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Tip programabil |

În sistem programabil |

|

Timp de întârziere TPD (1) Max |

7,5 ns |

|

Alimentare de tensiune - intern |

4.75V ~ 5.25V |

|

Numărul de elemente/blocuri logice |

4 |

|

Numărul de macroceluri |

64 |

|

Numărul de porți |

1250 |

|

Numărul de I/O. |

68 |

|

Temperatura de funcționare |

0 ° C ~ 70 ° C (TA) |

|

Tip de montare |

Montare la suprafață |

|

Pachet / carcasă |

100-TQFP |

|

Pachet de dispozitive furnizor |

100-TQFP (14x14) |

|

Numărul produsului de bază |

EPM7064 |

EPM7064STC100-7 Secvență de programare în sistem (ISP)

EPM7064STC100-7, o parte din familia CPLD Max 7000S, urmărește o secvență de programare în șase etape (ISP) pentru a asigura o configurație corectă.Acest proces vă permite să programați dispozitivul fără a -l scoate de pe placa de circuit.Procesul ISP implică schimbarea instrucțiunilor, adreselor și datelor prin intermediul PIN -ului TDI (Test in) în timp ce preia răspunsuri prin intermediul pinului TDO (test Out).

Prima etapă, Introduceți ISP, se asigură că pinii I/O tranziția fără probleme de la modul utilizator la modul ISP și necesită aproximativ 1ms.Aceasta este urmată de Verificați ID, unde este citit ID -ul de siliciu al dispozitivului pentru a confirma ținta corectă.Apoi, Ștergere în vrac STAGE SHINGS în instrucțiunile de ștergere și aplică un impuls de ștergere de 100ms, ștergând toate datele existente în celulele EEPROM. Program Urmează etapa, unde adresele și datele sunt schimbate secvențial în dispozitiv, aplicând impulsuri de programare pentru a configura celulele EEPROM.Fiecare adresă trebuie programată individual, ceea ce face ca acest pas să consume timp în funcție de numărul de celule EEPROM din dispozitiv.

Odată ce programarea este completă, Verifica Etapa asigură că datele au fost stocate corect.Aici, impulsurile citite sunt aplicate celulelor EEPROM, iar datele preluate sunt comparate cu valorile așteptate.Dacă se găsesc discrepanțe, poate fi necesară reprogramarea.În cele din urmă, Ieșiți ISP Etapa asigură trecerea pinilor I/O înapoi la modul utilizator, necesitând alte 1ms.Timpul total de programare sau verificare este influențat de doi factori principali: timpul de puls, necesar pentru ștergerea EEPROM, programarea și citirea operațiunilor și timpul de schimbare, care depinde de frecvența TCK (ceas de testare) și de numărul de cicluri necesare pentru transferul instrucțiunilor, adreselor și datelor.Deoarece diferite dispozitive capabile ISP au un număr diferit de celule EEPROM, atât timpii fixi și variabili totali sunt unici pentru fiecare dispozitiv.Timpul total ISP poate fi calculat ca funcție a frecvenței TCK, a numărului de dispozitive țintă și a arhitecturii EEPROM.

Aplicații EPM7064STC100-7

Sisteme încorporate

EPM7064STC100-7 este utilizat pe scară largă în aplicațiile de sistem încorporate, unde servește ca o soluție logică programabilă flexibilă pentru controlul diverselor periferice, semnale de procesare și implementarea protocoalelor personalizate.Capacitatea sa de a interfața cu microcontrolerele și senzorii permite optimizarea performanței sistemului, menținând în același timp o amprentă compactă.Cu funcționarea sa de mare viteză și consumul redus de energie, este o alegere excelentă pentru aplicațiile încorporate care necesită fiabilitate și eficiență.

Prelucrarea digitală a semnalului (DSP)

În procesarea digitală a semnalului, EPM7064STC100-7 joacă un rol în implementarea filtrelor, modularea semnalului și diverse funcții matematice.Vitezele sale de comutare rapidă și întârzierea de propagare scăzută o fac potrivită pentru gestionarea sarcinilor de prelucrare a datelor de înaltă frecvență, asigurând o latență minimă în conversia și manipularea semnalului.Este utilizat în mod obișnuit în sistemele de procesare audio, telecomunicații și radar.

Comunicări de date

EPM7064STC100-7 este utilizat pe scară largă în sistemele de comunicații în rețea și date, datorită capacității sale de a gestiona operațiuni intensive de logică, cum ar fi rutarea datelor, tamponarea și corectarea erorilor.Capacitățile sale de I/O programabile îi permit să se adapteze la diferite protocoale de comunicare, ceea ce îl face o componentă valoroasă în comutatoarele Ethernet, routere și infrastructura de telecomunicații.Suportul său pentru programabilitatea în sistem (ISP) permite, de asemenea, actualizări de câmp, îmbunătățind adaptabilitatea în mediile dinamice de rețea.

Automatizare industrială

Aplicațiile industriale necesită o fiabilitate ridicată, durabilitate și consum redus de energie, ceea ce face ca EPM7064STC100-7 să fie o alegere preferată pentru controlerele logice programabile (PLC), sisteme de control al motorului și echipamente de testare automate.Cu programabilitatea sa în sistem bazată pe JTAG, oferă capacitatea de a rafina procesele de automatizare fără a necesita îndepărtarea fizică sau reproiectarea.Versatilitatea sa în compatibilitatea tensiunii o face, de asemenea, potrivită pentru interfațarea cu o gamă largă de senzori și actuatoare utilizate în setări industriale.

EPM7064STC100-7 Piese similare

EPM7064STC100-7 Avantaje

Programmabilitate în sistem (ISP)

Unul dintre cele mai mari avantaje ale EPM7064STC100-7 este capacitatea sa de a fi reprogramat în timp ce este încă montat în sistem.Acest lucru elimină necesitatea eliminării cipului pentru actualizări, reducerea timpului de întreținere și îmbunătățirea eficienței.Puteți implementa modificări de proiectare fără a întrerupe producția, ceea ce o face o soluție rentabilă pentru proiectele pe termen lung.

Performanță de mare viteză

Dispozitivul acceptă o frecvență de funcționare internă ridicată de până la 166,7 MHz, permițând prelucrarea rapidă a datelor și timpii de răspuns.Acest lucru îl face ideal pentru aplicațiile care necesită procesarea semnalului, controlul logic și interfața de mare viteză, asigurând o funcționare a sistemului mai netedă și mai fiabilă.

Suport I/O versatil

Cu până la 68 de pini de I/O configurabili și compatibilitate cu mai multe niveluri de tensiune (3,3V, 5V și opțiuni tolerante pentru 2,5V, 3.3V și 5V), EPM7064STC100-7 oferă flexibilitate în proiectarea sistemului.Permite integrarea perfectă în diferite circuite și susține medii de tensiune mixtă, reducând problemele de compatibilitate cu alte componente.

Funcționare fiabilă în medii

Proiectat pentru a funcționa într-un interval de temperatură de la 0 ° C la 70 ° C, EPM7064STC100-7 asigură o funcționare constantă și stabilă într-o varietate de condiții.Această fiabilitate face o alegere preferată pentru aplicațiile în care este necesară stabilitatea mediului, cum ar fi automatizarea industrială, telecomunicațiile și sistemele de control încorporate.

EPM7064STC100-7 Schema de pachete

EPM7064STC100-7 este un CPLD (dispozitiv logic programabil complex) din seria Max 7000s a Altera, adăpostită într-un pachet plat subțire de 100 de pini (TQFP-100).Acest tip de pachet este proiectat pentru aplicații de montare a suprafeței, oferind un echilibru de densitate ridicată a pinului și dimensiune compactă. diagrama de pin-out Urmează o schemă de numerotare în sens invers acelor de ceasornic, cu pinul 1 situat în colțul din stânga sus al pachetului.Înălțând în sens invers acelor de ceasornic, primii 25 de pini ocupă partea stângă, pinii 26 până la 50 sunt poziționați de -a lungul marginii de jos, pinii 51 până la 75 continuă de -a lungul părții drepte, iar pinii 76 până la 100 sunt distribuiți de -a lungul marginii superioare. Pachet TQFP-100 Caracteristici plumburi subțiri care se extind spre exterior din toate cele patru părți ale corpului plat, pătrat.Acest design îmbunătățește compatibilitatea montată la suprafață, menținând în același timp o distanțare adecvată a pinului pentru lipirea și asamblarea ușoară.Pasul de plumb (distanța dintre pinii adiacenți) este de obicei de 0,5 mm, optimizând integritatea semnalului în timp ce minimizând amprenta generală.

EPM7064STC100-7 Producător

EPM7064STC100-7 este un CPLD (dispozitiv logic programabil complex) dezvoltat inițial de Altera, o companie semiconductor cunoscută pentru soluțiile sale logice programabile.În 2015, Intel a achiziționat ALTERA, integrându -și liniile de produse FPGA și CPLD în Grupul de soluții programabile Intel (PSG).De atunci, EPM7064STC100-7 a fost marcat sub Intel, deși a fost marcat ca învechit.Intel, în calitate de producător, a menținut asistența moștenită pentru CPLD -urile din seria Max® 7000S, inclusiv acest model, în timp ce își schimbă treptat atenția către FPGA modernă și tehnologii logice programabile.

Concluzie

EPM7064STC100-7 reunește funcții complexe, performanță rapidă și actualizări ușoare într-un singur cip, dovedindu-și valoarea în configurații digitale provocatoare.Acest ghid a arătat cum funcționează, pentru ce este folosit și cum se încadrează în diverse sisteme electronice.Ajută la realizarea dispozitivelor să funcționeze fără probleme și eficient, dovedind că este încă foarte util pentru multe aplicații.Acest ghid oferă o vedere clară a modului în care EPM7064STC100-7 poate ajuta la îmbunătățirea proiectelor electronice și a operațiunilor de sistem în mod eficient.

Fișă de date pdf

EPM7064STC100-7 Fisa de date:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Cum are întârzierea de propagare 7.5ns a performanței circuitului de impact EPM7064STC100-7?

O întârziere de propagare de 7,5ns asigură procesarea semnalului cu latență scăzută, ceea ce face ca acest CPLD să fie potrivit pentru aplicații de mare viteză, cum ar fi procesarea digitală a semnalului (DSP), sisteme de comunicare și automatizare industrială care necesită un control precis al calendarului.

2. Poate fi programat EPM7064STC100-7 folosind instrumente de dezvoltare modernă?

Da, poate fi programat folosind software -ul Intel Quartus II (fost Altera Quartus) împreună cu un programator JTAG adecvat.Cu toate acestea, suportul pentru CPLD-uri mai vechi, cum ar fi EPM7064STC100-7, poate fi limitat în versiunile mai noi Quartus, astfel încât este posibil să fie nevoie să utilizați versiuni vechi precum Quartus II 13.0 SP1, care încă acceptă dispozitive din seria Max® 7000S.

3. EPM7064STC100-7 acceptă medii de tensiune mixtă?

Da, acceptă atât nivelul logic de 3.3V cât și 5V, ceea ce îl face compatibil cu o gamă largă de circuite digitale.Această flexibilitate este utilă pentru interfațarea componentelor moștenite 5V cu sisteme moderne de 3.3V fără circuite suplimentare de schimbare a nivelului.

4. Care este cea mai bună metodă pentru depanarea unui design bazat pe EPM7064STC100-7?

Pentru a rezolva probleme, puteți utiliza analizatorul logic Quartus SignalTap II sau osciloscopurile externe și analizoarele logice pentru a monitoriza semnalele.Dacă depanați problemele de programare JTAG, asigurați -vă că conexiunile TDI, TDO, TCK și TMS sunt corecte și că utilizați un programator compatibil USB Blaster sau ByteBlastermv.

5. Pot programa EPM7064STC100-7 fără a-l scoate de pe placa de circuit?

Da.Programabilitatea în sistem 5.0V (ISP) prin JTAG (IEEE 1149.1) vă permite să reprogramați dispozitivul în timp ce acesta rămâne în sistem.Acest lucru face ca actualizările firmware -ului, depanarea și testarea mult mai eficientă în comparație cu CPLD -urile tradiționale.

Ghid complet pentru rezistența 10K: cod de culoare, aplicații și utilizări ale circuitului

pe 2025/03/10

Condensatori vs. Baterii: Care este cel mai bun pentru nevoile dvs. de energie?

pe 2025/03/7

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147770

-

Pinut și caracteristici USB-C

pe 2000/04/18 112006

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111351

-

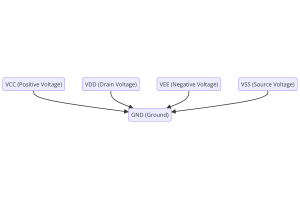

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83768

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79561

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66958

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63098

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63040

-

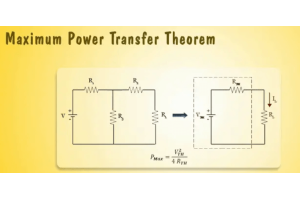

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54095

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52182