Ghid EPM7256SQC208-10: Caracteristici, PINOUT, programare, aplicații și fișă de date

Acest ghid se referă la EPM7256SQC208-10, un tip de cip programabil realizat de Intel (inițial de Altera).Provine din familia Max® 7000s și este cunoscut pentru a fi rapid, fiabil și ușor de programat în timp ce se află deja în interiorul unui dispozitiv.Acest articol explică ce face cipul, cum funcționează, unde este folosit și de ce este o alegere excelentă dacă aveți nevoie de un dispozitiv logic puternic și flexibil pentru proiectul dvs.Catalog

Prezentare generală a EPM7256SQC208-10

EPM7256SQC208-10 face parte din familia Intel (fosta Altera) Max® 7000S, o gamă CPLD de înaltă performanță, cunoscută pentru capacitățile sale robuste de programabilitate și optimizare logică.Acest model se mândrește cu aproximativ 5.000 de porți utilizabile și include 256 de macroceluri, adăpostite într-un pachet plat cu plastic cu 208 pini (PQFP).Funcționează la o frecvență de până la 128,2 MHz și acceptă o tensiune de funcționare de 5,0 V, cu o întârziere maximă de propagare de 7,5 ns și un plafon de temperatură operațional de +70 ° C.O caracteristică cheie este programabilitatea sa în sistem printr-un IEEE STD încorporat.1149.1 Interfață JTAG, permițând configurația dinamică.Dispozitivele Max® 7000S sunt fabricate folosind tehnologia CMOS avansată, oferind funcții precum întârzieri logice cu pin-to-pin la fel de rapid ca 5 NS și frecvențe de contor, care ajung până la 175,4 MHz.Familia prezintă o varietate de opțiuni de pachete și este proiectată cu flăcări programabile Macrocell care contribuie la economii substanțiale de putere de peste 50% în unele cazuri.În plus, include un bit de securitate pentru protecția proiectelor proprii.

Dacă organizația dvs. are nevoie de o soluție logică programabilă solidă, EPM7256SQC208-10 este o alegere fiabilă, așa că contactați-ne astăzi pentru a vă asigura comanda în vrac.

EPM7256SQC208-10 Modele CAD

Simbol EPM7256SQC208-10

EPM7256SQC208-10 Amprentă

EPM7256SQC208-10 Model 3D

Caracteristici EPM7256SQC208-10

• Densitate logică ridicată: EPM7256SQC208-10 oferă aproximativ 5.000 de porți utilizabile și conține 256 de macroceluri.Această capacitate logică ridicată o face ideală pentru implementarea circuitelor combinative complexe și integrarea logică eficientă în proiectele compacte.

• Performanță rapidă: Cu o frecvență de funcționare maximă de 128,2 MHz și o întârziere de propagare de doar 7,5 ns, acest CPLD asigură procesarea rapidă și timpii de răspuns rapid, buni pentru aplicații de mare viteză.

• Programmabilitate în sistem (ISP): Echipat cu un IEEE Std.1149.1 Interfață JTAG, dispozitivul permite programarea și testarea în sistem, fără a fi nevoie de îndepărtare fizică, facilitând dezvoltarea și actualizările iterative.

• Arhitectură avansată: Utilizarea arhitecturii Max de a doua generație a Altera și fabricat cu tehnologie CMOS avansată, EPM7256SQC208-10 oferă performanțe și durabilitate sporite, asigurând fiabilitatea în diverse medii operaționale.

• Gestionarea puterii: Dispozitivul oferă moduri programabile de economisire a energiei care pot reduce consumul de energie cu peste 50% pe macrocell, sprijinind proiectele eficiente din punct de vedere energetic și prelungind durata de viață a bateriei în aplicații portabile.

• Caracteristici de securitate: Un bit de securitate programabil oferă protecție împotriva accesului neautorizat și copierii proiectelor proprii, protejarea în mod eficient a proprietății intelectuale.

• Condiții de operare largi: Funcționând la 5,0 V și capabil să funcționeze la temperaturi de până la +70 ° C, acest CPLD se adaptează la condiții de mediu diverse, ceea ce îl face adecvat atât pentru aplicații industriale, cât și comerciale.

• Standarde I/O flexibile : Acceptă operațiunile de interfață I/O MultiVolt ™, compatibile atât cu sistemele de 3,3 V cât și cu 5,0 V.Această flexibilitate permite o integrare perfectă cu hardware -ul existent și nou, reducând complexitatea și costurile sistemului.

• Suport de proiectare: EPM7256SQC208-10 este acceptat de o serie de instrumente de proiectare și opțiuni hardware de programare, simplificând procesul de dezvoltare și permițând să se concentreze pe inovație, mai degrabă decât pe probleme de compatibilitate.

EPM7256SQC208-10 Diagrama PINOUT

Această diagramă arată aspectul pinului pentru cipul EPM7256SQC208-10 de la Altera.Cipul are 208 de pini, aranjați pe toate cele patru laturi într -o formă pătrată.Pinul 1 pornește din colțul din stânga sus și numerele se înconjoară în jurul cipului într-o direcție în sens invers acelor de ceasornic, în partea stângă spre pinul 53, pe partea de jos pentru a pin 105, în partea dreaptă până la pinul 157 și înapoi în partea dreaptă sus.Etichetele vă ajută să știți de unde să începeți și cum să așezați cipul corect pe o placă de circuit.Numele din centru, „EPM7256E / EPM7256S”, înseamnă că acest aspect funcționează pentru ambele versiuni CIP.Această diagramă este importantă atunci când conectați puterea, semnalele sau liniile de programare la cip.

EPM7256SQC208-10 Diagrama blocului

Diagrama bloc a EPM7256SQC208-10 arată cum este organizat cipul pentru a gestiona sarcinile logice digitale.Are patru blocuri logice principale numite Laborator A, B, C și D. Fiecare bloc conține 16 macroceluri, care sunt piesele de construcție de bază care fac lucrările logice.Deci, în total, există 64 de macroceluri în interiorul cipului.În jurul acestor blocuri logice sunt blocuri de control I/O, care conectează cipul la lumea exterioară prin intermediul pinilor de intrare și ieșire.Fiecare bloc de control gestionează 6 până la 16 pini, lăsând semnalele să intre sau să iasă din cip, după cum este necesar.

În centru se află tabloul de interconectare programabil (PIA), care acționează ca un sistem de autostradă, permițând semnalele să se deplaseze între blocurile logice și pinii I/O.Acest lucru vă permite să dirijați datele în orice mod aveți nevoie pentru proiectarea dvs.În stânga sus, diagrama prezintă unele intrări de control precum Global Clock (GCLK), Activare de ieșire (OE) și Clear (GCLR).Aceste semnale ajută la gestionarea calendarului și a comportamentului circuitelor logice de pe cip.

Specificații EPM7256SQC208-10

|

Tip |

Parametru |

|

Producător |

Alterra/Intel |

|

Serie |

Max® 7000s |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Tip programabil |

În sistem programabil |

|

Timp de întârziere TPD (1) Max |

10 ns |

|

Alimentare de tensiune - intern |

4.75V ~ 5.25V |

|

Numărul de elemente/blocuri logice |

16 |

|

Numărul de macroceluri |

256 |

|

Numărul de porți |

5000 |

|

Numărul de I/O. |

164 |

|

Temperatura de funcționare |

0 ° C ~ 70 ° C (TA) |

|

Tip de montare |

Montare la suprafață |

|

Pachet / carcasă |

208-BFQFP |

|

Pachet de dispozitive furnizor |

208-PQFP (28x28) |

|

Numărul produsului de bază |

EPM7256 |

Aplicații EPM7256SQC208-10

Automatizare industrială

EPM7256SQC208-10 este utilizat pe scară largă în sistemele de automatizare industrială.Densitatea sa logică ridicată și performanța rapidă permit sarcini complexe de control, interfațând perfect cu senzori și actuatori.Acest CPLD este ideal pentru îmbunătățirea preciziei și eficienței în liniile de producție, sistemele de control al proceselor și aplicațiile robotice.

Telecomunicații

În telecomunicații, acest CPLD excelează în gestionarea fluxului de date și a integrității semnalului în rețele.Suportă funcții precum conversia semnalului, rutarea și procesarea în comutatoare și routere, asigurând infrastructuri de comunicare robuste și eficiente.

Sisteme auto

În industria auto, acest dispozitiv contribuie la fiabilitatea și sofisticarea sistemelor precum unitățile de gestionare a motoarelor, sistemele de infotainment și tehnologiile de asistență a șoferilor.Performanța sa robustă în condiții variate o face potrivită pentru aplicații critice pentru siguranță.

Dispozitive medicale

Precizia și programabilitatea EPM7256SQC208-10 o fac valoroasă în echipamentele medicale, unde sunt importante un control precis și o funcționare fiabilă.Este utilizat în dispozitive pentru monitorizarea vitalelor pacientului, gestionarea instrumentelor de diagnostic și automatizarea administrării tratamentului.

Aerospațial și apărare

În aerospațial și apărare, EPM7256SQC208-10 este utilizat în sisteme care necesită un nivel ridicat de fiabilitate și performanță, cum ar fi comunicații prin satelit, ajutoare de navigație și controale hardware militare.Capacitatea sa de a opera în condiții extreme este benefică.

Instituții educaționale și de cercetare

Acest CPLD este popular și în setările educaționale și în proiectele de cercetare, unde reprogramabilitatea și flexibilitatea sa facilitează experimentarea și învățarea în proiectarea digitală și electronica.Permite prototip și testarea diferitelor proiecte logice în mod eficient.

EPM7256SQC208-10 Piese similare

EPM7256SQC208-10 Pași de programare

1. Introduceți modul ISP

Această etapă inițială este importantă, deoarece tranziționează CPLD de la modul normal de funcționare la modul de programare în sistem (ISP).Acest lucru se realizează prin trimiterea unei comandă specifică prin interfața JTAG.În timpul acestui proces, toți pinii I/O ale CPLD sunt tri-declarați (dezactivați) pentru a evita orice interferență sau conflicte cu alte componente ale circuitului.Tranziția în modul ISP pregătește dispozitivul pentru o programare sigură și durează aproximativ 1 milisecundă.

2. Verificați ID -ul

Odată în modul ISP, sistemul efectuează o verificare ID pentru a se asigura că dispozitivul corect este programat.Aceasta implică citirea ID -ului unic de siliciu al dispozitivului prin interfața JTAG.Acest pas este bun pentru a verifica dacă comenzile și datele de programare vor fi trimise către dispozitivul corect, prevenind programarea eronată și deteriorarea potențială a dispozitivului.

3. Ștergerea în vrac

Înainte de a putea fi programate date noi, datele existente în cadrul CPLD trebuie șterse.Pasul de ștergere în vrac șterge în mod eficient toate celulele programabile din dispozitiv.Acest lucru se realizează prin schimbarea instrucțiunilor de ștergere și apoi aplicarea unui impuls de 100 de milisecunde care șterge întregul cip.Această etapă este importantă pentru a se asigura că nu există resturi de configurații anterioare cu noua programare.

4. Program

Acest pas implică programarea reală a CPLD în care noile date de configurare sunt scrise în dispozitiv.Datele și adresele corespunzătoare sunt schimbate în dispozitiv prin interfața JTAG.Fiecare adresă și pereche de date necesită un impuls de programare pentru a se asigura că datele sunt scrise corect în celulele de memorie non-volatile ale CPLD.Acest pas este repetat pentru fiecare punct de date pe harta memoriei dispozitivului.

5. Verificați

Post-programare, este necesar să verificați dacă datele au fost scrise corect pe dispozitiv.Această etapă de verificare implică citirea înapoi a datelor programate de la fiecare adresă și compararea acesteia cu datele de intrare originale.Acest pas asigură integritatea datelor și confirmă faptul că procesul de programare a avut succes fără erori.

6. Ieșiți în modul ISP

Ultimul pas în procesul de programare este să ieșiți din modul ISP și să returnați CPLD în modul operațional normal.Acest lucru se realizează prin trimiterea unei alte comandă prin intermediul interfeței JTAG.La ieșirea cu succes, pinii I/O sunt reactivați, iar dispozitivul reia funcția normală.De asemenea, acest pas durează de obicei aproximativ 1 milisecundă.

EPM7256SQC208-10 Avantaje

Configurare non-volatilă

EPM7256SQC208-10 utilizează tehnologia EEPROM, permițându-i să stocheze configurația permanentă.Această natură non-volatilă înseamnă că dispozitivul nu trebuie să reîncărce datele sale de configurare din memoria externă de fiecare dată când este pornit.Acest lucru duce la perioade de pornire mai rapide și reduce complexitatea generală a designului hardware, eliminând necesitatea unor componente suplimentare de stocare a configurației.

Programmabilitate în sistem (ISP)

Una dintre caracteristicile deosebite ale EPM7256SQC208-10 este sprijinul său pentru programabilitatea în sistem.Acest lucru permite programarea și reprogramarea dispozitivului în timp ce este încorporată în aplicația finală, fără a fi nevoie să fie eliminat fizic.Această capacitate simplifică actualizările și modificările, oferind flexibilitate și ușurință de utilizare în timpul dezvoltării și pe tot parcursul ciclului de viață al produsului.

Număr ridicat de I/O și densitate logică

Dispozitivul oferă o cantitate substanțială de resurse logice și pini I/O, cu 256 de macroceluri și 164 pini de utilizator I/O.Acest număr ridicat de I/O și densitatea logică permite integrarea mai multor funcții într -un singur cip, facilitând modele mai complexe în timp ce conservă spațiul pe PCB.Acest avantaj este benefic în aplicațiile în care spațiul consiliului de administrație este la o primă și multifuncționalitatea este importantă.

Întârziere rapidă cu pin-to-pin

Cu o întârziere maximă cu pin-to-pin de doar 10 ns, EPM7256SQC208-10 poate efectua operații logice de mare viteză.Acest timp de răspuns rapid este excelent în aplicațiile care necesită capacități de procesare rapidă, cum ar fi comunicații de mare viteză sau calcul, asigurându-se că sistemul îndeplinește criterii de performanță stricte.

Compatibilitatea largă a tensiunii

EPM7256SQC208-10 este proiectat pentru a fi flexibil în ceea ce privește compatibilitatea tensiunii, susținând funcționarea internă la niveluri de 5 V și I/O la 3.3 V. Această capacitate de dublă tensiune permite dispozitivului să interfațăm ușor atât cu sistemele 3.3 V, cât și cu 5 V, reducând nevoia de traducători la nivel de tensiune, cât și cu proiectarea sistemului.

EPM7256SQC208-10 Dimensiuni de ambalare

• Tip de pachet: 208-BFQFP (pachet plat cu plastic quad)

• Numărul de pini: 208 conduce

• Mărimea corpului (L × W): 28 mm × 28 mm

• Stil de montare: Tehnologia de montare a suprafeței (SMT)

• Place Pitch: De obicei 0,5 mm între pini (standard pentru BFQFP)

• Material de pachet: Plastic

• Grosimea pachetului: Aproximativ 3,5 mm (variază ușor în funcție de producător)

• Caracteristici termice: Fără tampon expus;disiparea standard ambientală prin placă

• Ambalaj de tavă: Furnizată în tăvi pentru manipularea volumului și automatizarea preluării și a locului

EPM7256SQC208-10 Producător

EPM7256SQC208-10 a fost inițial dezvoltat și fabricat de Altera Corporation, un pionier principal în dispozitivele logice programabile cunoscute pentru seria sa Max® 7000s de CPLDS.În 2015, Altera a fost achiziționată de Intel Corporation, unul dintre cei mai mari producători de semiconductori din lume.De la achiziție, Intel a continuat să susțină și să integreze tehnologiile CPLD și FPGA ale Altera în cadrul grupului său de soluții programabile.EPM7256SQC208-10 reprezintă moștenirea Intel în a oferi soluții logice programabile în sistem de înaltă performanță, adaptate pentru o gamă largă de aplicații industriale, telecomunicații și încorporate.Deși acum este clasificată ca învechită, partea reflectă angajamentul de lungă durată al Intel față de dispozitivele logice programabile fiabile și flexibile.

Concluzie

EPM7256SQC208-10 este un cip inteligent și de încredere, care ajută la ca sistemele digitale să funcționeze fără probleme.Salvează puterea, acceptă diferite tensiuni și vă permite să o programați în timp ce este deja instalat, ceea ce face actualizări ușoare.Chiar dacă acum este un cip mai vechi, alții îl folosesc în continuare, deoarece funcționează bine în toate tipurile de sisteme.Dacă aveți nevoie de un cip solid pentru controlul logicii în designul dvs., aceasta este o opțiune excelentă.Contactați -ne astăzi dacă doriți să o comandați în vrac.

Fișă de date pdf

Fișiere de date EPM7256SQC208-10:

Suport pentru baterii cilindrice.pdf

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Ce instrumente de programare sunt compatibile cu EPM7256SQC208-10?

Puteți utiliza software-ul Intel Quartus II (fostul Altera Quartus), împreună cu un programator compatibil cu JTAG, precum USB-Blaster, pentru a configura și programa direct EPM7256SQC208-10 direct în sistem.

2. Pot reprograma EPM7256SQC208-10 de mai multe ori?

Da, EPM7256SQC208-10 acceptă mai multe cicluri de reprogramare folosind programabilitatea sa în sistem bazată pe EEPROM, ceea ce îl face ideal pentru dezvoltarea designului iterativ sau actualizări post-implementare.

3. Poate EPM7256SQC208-10 să gestioneze condiții dure de operare?

Funcționează în mod fiabil într-un interval de temperatură comercial de la 0 ° C până la +70 ° C, ceea ce este suficient pentru majoritatea aplicațiilor industriale și încorporate, deși nu pentru medii extreme sau de calitate auto.

4. Mai pot programa EPM7256SQC208-10 fără a-l elimina de pe placa de circuit?

Da.CHIP acceptă programabilitatea în sistem (ISP) prin JTAG, permițându-vă să o reprogramați în timp ce este deja lipit pe placa dvs., economisind timp și efort în timpul dezvoltării sau întreținerii.

5. Ce face EPM7256SQC208-10 mai bun decât un microcontroller standard pentru sarcini logice?

Spre deosebire de microcontrolere, EPM7256SQC208-10 este un CPLD, care excelează la executarea operațiunilor logice paralele cu sincronizare precisă.Este ideal atunci când aveți nevoie de un control digital rapid și determinist asupra mai multor semnale.

Teoremele lui DeMorgan explicate: simplificarea expresiilor logice pentru un design mai bun circuit

pe 2025/04/25

Elementele de bază și exemple de circuit al teoremei Norton

pe 2025/04/24

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147765

-

Pinut și caracteristici USB-C

pe 2000/04/18 111994

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111351

-

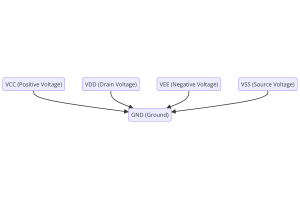

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83751

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79548

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66949

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63094

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63028

-

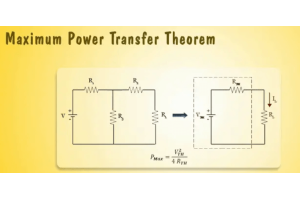

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54094

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52175