LFEC3E-3Q208C Prezentare generală FPGA: Caracteristici, aplicații, programare și specificații

În acest articol, veți afla despre LFEC3E-3Q208C, un FPGA de la semiconductorul de lattice.Veți vedea despre ce este vorba, principalele caracteristici pe care le oferă și de ce este util pentru multe modele de gamă medie.Conținutul vă parcurge, de asemenea, prin specificațiile, aplicațiile și procesul de programare pas cu pas, împreună cu avantajele, contra și detaliile producătorului.Catalog

Ce este lfec3e-3q208c?

Lfec3e-3q208c este un tablou de poartă programabil de teren (FPGA) din punct de vedere al costurilor de la Lattice Semiconductor, proiectat ca parte a familiei Latticeec (Economy).Această familie a fost dezvoltată pentru a oferi soluții logice programabile care echilibrează accesibilitatea cu performanțe fiabile pentru proiectele mainstream.În cadrul ierarhiei Latticeec, acesta se află în intervalul mediu, oferind aproximativ 3.000 de elemente logice și o utilizare eficientă a puterii, reducând decalajul dintre dispozitivele de intrare mai mici și modele mai mari, mai intensiv în resurse.Seria mai largă de LatticeECP/CE subliniază programabilitatea, scalabilitatea și flexibilitatea cu costuri reduse pe mai multe dimensiuni ale dispozitivului, varianta CE concentrându-se pe performanța bazată pe economie.

Căutați lfec3e-3q208c?Contactați -ne pentru a verifica stocul curent, timpul de plumb și prețurile.

Caracteristici LFEC3E-3Q208C

• Resurse logice

Dispozitivul integrează aproximativ 3.100 de elemente logice organizate în 384 de blocuri, oferindu-i o capacitate suficientă pentru proiectele de gamă medie.Acest echilibru de resurse îl face potrivit pentru logica de control, procesarea semnalului și aplicații încorporate fără costuri excesive.

• I/O programabil

Cu până la 145 de pini de intrare/ieșire programabile, acceptă o mare varietate de opțiuni de conectivitate.Aceste I/OS sunt compatibile cu standarde multiple, cum ar fi LVCMOS, LVTTL, LVDS, PCI și SSTL, care permit integrarea flexibilă a sistemului.

• Memorie încorporată

FPGA include RAM bloc dedicat (EBR) și resurse RAM distribuite, oferind stocare eficientă pe cip.Acest lucru permite implementarea tamponului de date, a tabelelor de căutare sau a unor mici amintiri încorporate direct în interiorul dispozitivului.

• Gestionarea ceasului

Dispune de până la patru PLL -uri integrate, oferind înmulțirea frecvenței, diviziunea și schimbarea fazelor.Acest lucru permite controlul precis și sincronizarea cu privire la proiectele de mare viteză.

• Suport de memorie DDR

Dispozitivul include suport hardware pentru interfețele DDR, capabil să ruleze DDR400 (200 MHz).Acest lucru îl face practic pentru proiectele care necesită acces extern de memorie de mare viteză.

• Eficiența puterii

Funcționând cu o sursă de bază de 1,2 V, FPGA minimizează consumul general de energie a sistemului.Proiectarea sa cu putere redusă este ideală pentru aplicații portabile sau sensibile la energie.

• Caracteristici la nivel de sistem

Funcții încorporate, cum ar fi IEEE 1149.1 Scanarea de graniță, analiza logică pe cip (ISPTracy) și o interfață flash de pornire SPI simplifică testarea și depanarea.Aceste caracteristici reduc timpul de dezvoltare și îmbunătățesc fiabilitatea proiectării.

• Suport pentru dezvoltare

Suportat de IsPlever Design Suite, dispozitivul beneficiază de instrumente automate de sinteză, loc-și rută și de verificare.Puteți utiliza, de asemenea, blocuri IP IsPleverCore pentru a accelera funcțiile comune și pentru a scurta timp la piață.

Diagrama blocului familial LatticeECP/CE

Diagrama bloc a familiei LatticeECP/CE (inclusiv LFEC3E-3Q208C) arată cum este construit FPGA și cum funcționează părțile sale împreună.Celulele I/O programabile (PICS) sunt plasate în jurul marginilor pentru a conecta cipul cu dispozitivele exterioare, susținând multe standarde de semnal.În interior, unitățile funcționale programabile (PFUS) gestionează operațiunile logice, cu unele asociate cu RAM bloc încorporat (EBR) pentru stocarea datelor, iar altele s -au concentrat doar pe logică.SYSCLOCK PLLS gestionează semnalele de ceas, astfel încât designul să poată rula la viteza și momentul potrivit.Portul Sysconfig și portul JTAG vă permit să programați, să testați și să depanați FPGA cu ușurință.Acest aspect oferă flexibilitatea LFEC3E-3Q208C, performanță fiabilă și integrare simplă în proiectele sensibile la costuri.

Diagrama feliei de latticeecp/CE

Felia din familia LatticeECP/CE, ca în LFEC3E-3Q208C, este unitatea logică de bază care combină blocuri LUT4 și transport pentru efectuarea operațiunilor logice și aritmetice.Fiecare felie include, de asemenea, flip-flops/zăvoare pentru a stoca date și pentru a activa logica secvențială, cu multiplexori pentru a direcționa semnalele flexibile fie prin registre, fie direct.Această structură este importantă, deoarece oferă viteza, flexibilitatea și eficiența FPGA pentru a gestiona atât modele digitale simple, cât și complexe.Următorul tabel rezumă descrierile semnalului de felie, inclusiv funcțiile, tipurile, numele de semnal și scopurile lor.

|

Funcţie |

Tip |

Numele semnalului |

Descriere |

|

Intrare |

Semnal de date |

A0, B0, C0, D0 |

Intrări la LUT4 |

|

Intrare |

Semnal de date |

A1, B1, C1, D1 |

Intrări la LUT4 |

|

Intrare |

Polivalent |

M0 |

Intrare polivalentă |

|

Intrare |

Polivalent |

M1 |

Intrare polivalentă |

|

Intrare |

Semnal de control |

CE |

Activare ceas |

|

Intrare |

Semnal de control |

LSR |

Set/resetare locală |

|

Intrare |

Semnal de control |

Clk |

Ceas de sistem |

|

Intrare |

Semnal inter-PFU |

Fcin |

Purtați rapid in¹ |

|

Ieșire |

Semnale de date |

F0, F1 |

Semnalele de ocolire a registrului de ieșire LUT4 |

|

Ieșire |

Semnale de date |

Q0, Q1 |

Recorduri de înregistrare |

|

Ieșire |

Semnale de date |

Ofx0 |

Ieșirea unui MUX LUT5 |

|

Ieșire |

Semnale de date |

Ofx1 |

Ieșirea unui lut6, lut7, lut8 2 mux în funcție de felie |

|

Ieșire |

Semnal inter-PFU |

FCO |

Pentru cea mai bună PFU, ieșirea rapidă a lanțului de transport¹ |

Specificații LFEC3E-3Q208C

|

Tip |

Parametru |

|

Producător |

Semiconductor de zăpadă |

|

Tensiune - alimentare |

1.14V ~ 1.26V |

|

Biți de ram totale |

56.320 |

|

Pachet de dispozitive furnizor |

208-PQFP (28x28) |

|

Serie |

CE |

|

Pachet / carcasă |

208-BFQFP |

|

Pachet |

Tavă |

|

Temperatura de funcționare |

0 ° C ~ 85 ° C (TJ) |

|

Numărul de elemente/celule logice |

3.100 |

|

Numărul de I/O. |

145 |

|

Tip de montare |

Montare la suprafață |

|

Numărul produsului de bază |

Lfec3 |

Aplicații LFEC3E-3Q208C

1. Sisteme de control încorporate

LFEC3E-3Q208C este potrivit pentru controlerele încorporate în dispozitive, automatizarea industrială și gateway-urile IoT.Densitatea sa logică moderată și designul low-cost permit înlocuirea logicii cu funcții fixe cu flexibilitate programabilă.Acest lucru facilitează actualizarea sistemelor sau adaptarea la standardele în evoluție fără a reproiecta hardware -ul.

2. Interfațarea memoriei DDR

Cu suport încorporat pentru memoria DDR400, dispozitivul poate gestiona tamponarea datelor, logarea sau stocarea temporară în aplicații.Această caracteristică este utilă în sistemele în care viteza de memorie externă este importantă, dar nu este necesară performanța FPGA de înaltă calitate.Mulți beneficiază de un echilibru de viteză, costuri și eficiență a memoriei.

3. I/O Bridging și conversia protocolului

Datorită asistenței sale largi pentru standardele I/O, cum ar fi LVCMOS, LVTTL, LVDS, PCI și SSTL, FPGA este eficient pentru a reduce diferite interfețe digitale.Poate fi configurat pentru a traduce semnale între subsisteme, ceea ce îl face valoros în proiectele de tehnologie mixtă.Această flexibilitate ajută la prelungirea duratei de viață a hardware -ului existent, permițând compatibilitatea cu noi componente.

4. Aplicații industriale și de infrastructură

De asemenea, dispozitivul poate servi în echipamente industriale și de infrastructură sensibile la costuri, unde fiabilitatea și performanța moderată sunt suficiente.Sprijinul său pentru scanarea graniței, depanarea pe cip și funcționarea cu putere redusă îl fac ideal pentru sistemele care necesită eficiență și întreținere ușoară.Rolurile tipice includ unități de control, module de interfață și sisteme de monitorizare.

Lfec3e-3q208c Piese similare

|

Specificații |

Lfec3e-3q208c |

Lfec3e-3q208i |

Lfec3e-3qn208c |

Lfec3e-4q208c |

Lfec1e-3q208c

|

Lfec6e-3q208c

|

|

Elemente logice (LUTS) |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 1,5k |

~ 6.1k |

|

Blocuri logice |

384 |

384 |

384 |

384 |

192 |

768 |

|

RAM de bloc încorporat (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Frecvența de funcționare maximă |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

I/O Count |

145 |

145 |

145 |

145 |

112 |

145 |

|

Pachet |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

Tensiune de bază |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

Interval de temperatură |

0 ° C până la +70 ° C. |

–40 ° C până la +85 ° C. |

0 ° C până la +70 ° C. |

0 ° C până la +70 ° C. |

0 ° C până la +70 ° C. |

0 ° C până la +70 ° C. |

|

Tipul de conformitate / pachet |

Standard |

Industrial |

Fără plumb (QN) |

Variantă (Q) |

Standard |

Standard |

|

Aplicație |

Densitate medie, cu scop general |

La fel ca lfec3e, dar uz industrial |

La fel ca lfec3e, dar conform pachetului |

Aceeași familie, migrație ușoară |

Opțiune de cost de densitate mică |

Upgrade cu densitate mai mare |

Pași de programare LFEC3E-3Q208C

Înainte de a începe programarea LFEC3E-3Q208C, este important să pregătiți instrumentele potrivite și să înțelegeți fluxul de proiectare pentru configurația dispozitivului.Fiecare pas se bazează pe cea anterioară, astfel încât o atenție atentă va asigura un proces de programare lină.

1. Pregătiți hardware și software de programare

Începeți prin instalarea sistemului de diamante sau a sistemului ISPVM al Lattice, care sunt instrumentele oficiale pentru acest FPGA.Apoi, configurați cablul de programare JTAG, cum ar fi HW-USBN-2B și asigurați-vă că driverele sunt instalate corespunzător.Acest pas se asigură că computerul dvs. este gata să comunice cu dispozitivul țintă fără erori de conectare.

2. Implementați -vă proiectarea în software -ul de dezvoltare

În continuare, creați un nou proiect în Lattice Diamond și selectați LFEC3E-3Q208C ca dispozitiv țintă.Apoi adăugați fișierele sursă Verilog sau VHDL, aplicați atribuții PIN și definiți orice constrângeri de sincronizare.După ce s-a terminat, sintetizați designul, efectuați loc și rute și, în sfârșit, generați fișierul bitstream (.bit sau .Jed) care va fi utilizat pentru programare.

3. Configurați placa și conexiunile

Acum, conectați cablul JTAG la placa FPGA, asigurându -vă că conexiunea la sol este sigură înainte de a atașa liniile de semnal.Confirmați că rezistențele de tragere și derulare sunt corecte, în special pe TCK și pe liniile de scurgere deschisă.Dacă placa dvs. are pini de control suplimentari, cum ar fi ERASE sau ISPEN, trebuie să le configurați corect pentru a preveni resetările accidentale în timpul programării.

4. Programează dispozitivul

Cu hardware -ul gata, lansați instrumentul de programare și selectați cablul conectat.Încărcați fișierul bitstream generat și alegeți modul corespunzător, de obicei JTAG, în funcție de configurarea dvs.Porniți procesul de programare, iar instrumentul va configura FPGA în timp ce verifică dacă datele au fost scrise corect.

5. Verificați și depanați configurația

După programare, verificați pinii terminați sau init pe placa dvs. pentru a confirma că FPGA a configurat cu succes.Dacă este necesar, utilizați ISPTracy Logic Analyzer sau funcții de scanare a graniței pentru a testa funcționalitatea și validați comportamentul semnalului.Puteți repeta ciclul de proiectare și programare ori de câte ori sunt necesare modificări, asigurându -vă că proiectul dvs. este rafinat pas cu pas.

LFEC3E-3Q208C Avantaje și dezavantaje

Avantaje

• Consum redus de energie electrică, potrivit pentru proiectări sensibile la energie

• rentabil în comparație cu FPGA-urile superioare

• Chain de instrumente simple cu o curbă de învățare mai ușoară

• Reconfigurabil pe câmp pentru actualizări după implementare

• Pachet compact cu un echilibru bun de resurse

Dezavantaje

• Performanță limitată în comparație cu FPGA mai mare

• Logică mai mică și capacitate de memorie decât dispozitivele de înaltă calitate

• Mai puține nuclee IP terțe și asistență ecosistemică

• Toolchain nu are caracteristici avansate ale majorilor furnizori

• Nu este potrivit pentru interfețe cu viteză ultra-înaltă

Dimensiuni de ambalare LFEC3E-3Q208C

|

Tip |

Parametru |

|

Tip de pachet |

208-PQFP (pachet de plastic quad plat) |

|

Dimensiunea corpului |

28 mm × 28 mm |

|

Pas |

0,5 mm |

|

Înălțimea pachetului (max) |

~ 3,4 mm |

|

Număr de plumb |

208 pini |

|

Stil de pachet |

Plumburi de aripi de pescăruș (quad) |

|

Tip de montare |

Montare la suprafață |

|

Cod de caz |

BFQFP-208 |

|

Pachet de furnizori |

Tavă |

Producător LFEC3E-3Q208C

LFEC3E-3Q208C este fabricat de Lattice Semiconductor Corporation , o companie din SUA cu sediul central în Hillsboro, Oregon.Înființată în 1983, Lattice este specializată în dezvoltarea unor tablouri de poartă programabile cu putere redusă, eficientă din punct de vedere al costurilor (FPGA) și soluții conexe.Compania se concentrează pe activarea aplicațiilor în comunicații, calcule, electronice de consum, piețe industriale și auto.Cunoscut pentru inovația sa în dispozitivele programabile eficiente din punct de vedere energetic, Lattice s-a stabilit ca un jucător cheie în industria FPGA, în special pentru proiectele care cer factori de formă compacte, consumul redus de energie și fiabilitate ridicată.

Concluzie

LFEC3E-3Q208C oferă un mix bun de costuri reduse, uzură redusă și suficientă logică și memorie pentru proiecte de gamă medie.Suportă multe standarde I/O, are RAM și PLL-uri încorporate și poate funcționa cu memoria DDR400, ceea ce îl face util pentru sarcini de control, interfață și industriale.Programarea este simplă cu instrumentele de zăbrele, iar caracteristicile de depanare suplimentare ajută la testare.Deși nu se poate potrivi cu viteza și capacitatea FPGA mai mare, este o alegere fiabilă pentru proiectele care au nevoie de flexibilitate, eficiență și performanță accesibilă.

Fișă de date pdf

Piese de date LFEC3E-3Q208C:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1.. LfeC3E-3Q208C acceptă interfețe de mare viteză precum PCIE sau Gigabit Ethernet?

Nr. LFEC3E-3Q208C este proiectat pentru aplicații mainstream și sensibile la costuri, deci nu include transceiver-uri seriale de mare viteză native.În schimb, se concentrează pe interfețe paralele și suport de memorie DDR.

2. Poate fi reprogramat lfec3e-3q208c după implementare?

Da.Ca FPGA, LFEC3E-3Q208C este complet reconfigurabil, permițând actualizări și modificări de proiectare chiar și după implementare.Această flexibilitate reduce costurile de întreținere pe termen lung și extinde ciclurile de viață a produsului.

3. Cum se ocupă LFEC3E-3Q208C depanarea și testarea?

Dispozitivul integrează scanarea graniței (IEEE 1149.1), analiza logică pe cip (ISPTracy) și suportul flash de pornire SPI.Aceste instrumente încorporate simplifică depanarea și reduc nevoia de hardware de testare externă.

4. Poate LFEC3E-3Q208C să prelungească durata de viață a sistemelor hardware mai vechi?

Da, datorită capacităților sale largi de compatibilitate I/O și a protocolului, poate interfața sistemele mai vechi cu componente mai noi, ajutând întreprinderile să extindă utilitatea hardware -ului existent.

5. Ce instrumente de programare sunt necesare pentru LFEC3E-3Q208C?

Este programat folosind programatorul de diamante sau sistemul ISPVM al Lattice.Aceste instrumente acceptă intrarea de proiectare, generarea bitstream și configurația dispozitivului, ceea ce face ca fluxul de lucru să fie simplificat.

AD73311LARS: fișă de date, funcții, PINOUT și Ghid de programare

pe 2025/08/28

EPM1270F256C4N MAX II II CPLD Prezentare generală: Caracteristici, specificații și aplicații

pe 2025/08/28

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/19 147782

-

Pinut și caracteristici USB-C

pe 2000/04/19 112070

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/19 111352

-

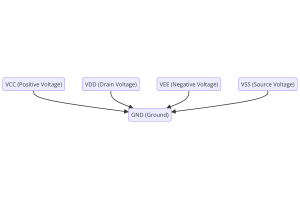

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/19 83829

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79642

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 67006

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63131

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63067

-

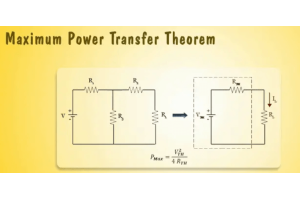

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54097

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52226