XC2S50-5TQG144I FPGA: Caracteristici, specificații, aplicații și ghid de programare

XC2S50-5TQG144I este un FPGA flexibil și puternic (tabloul de poartă programabil de câmp) din familia Spartan-II a AMD Xilinx.Este conceput pentru proiecte digitale care au nevoie de personalizare, viteză și fiabilitate.Acest ghid explică caracteristicile, specificațiile, procesul de programare și utilizările acestui FPGA pentru a vă ajuta să înțelegeți cum să profitați la maxim.Catalog

Prezentare generală XC2S50-5TQG144I

XC2S50-5TQG144I este un FPGA spartan-II de la AMD Xilinx, conceput pentru proiecte digitale care au nevoie de flexibilitate și performanță.Are 50.000 de porți de sistem și 1.728 de celule logice, permițându -i să gestioneze sarcini complexe.CIP -ul include 384 de blocuri logice configurabile (CLBS) și 32.768 biți RAM, oferindu -i o putere bună de memorie și procesare.Cu 92 pini de intrare/ieșire (I/O), se poate conecta cu ușurință la alte componente.Acesta vine într-un pachet plat subțire de 144 de pini (TQFP), care este compact și ușor de utilizat.FPGA rulează pe 2,5V (cu un interval sigur de 2,375V la 2.625V) și funcționează bine la temperaturi între -40 ° C și +100 ° C.Acest FPGA spartan-II este realizat cu tehnologie de 0,18-micron, ceea ce o face eficientă și fiabilă.Este programabil, ceea ce înseamnă că puteți actualiza funcțiile sale, după cum este necesar.

Pentru o soluție rentabilă, de înaltă performanță, plasarea unei comenzi în vrac cu noi este alegerea optimă, asigurând o calitate superioară.

Modele CAD XC2S50-5TQG144I

Simbol XC2S50-5TQG144I

XC2S50-5TQG144I Amprentă

XC2S50-5TQG144I MODEL 3D

Caracteristici XC2S50-5TQG144I

• Porți de sistem: XC2S50-5TQG144I FPGA oferă aproximativ 50.000 de porți ale sistemului.Acest lucru îi permite să sprijine proiecte și aplicații digitale complexe care necesită o cantitate substanțială de capacități de procesare logică.

• Celule logice: Acest dispozitiv include 1.728 de celule logice, care facilitează implementarea configurațiilor logice complexe și crearea diferitelor funcționalități digitale în cadrul FPGA.

• Blocuri logice configurabile (CLBS): Dispune de 384 de blocuri logice configurabile (CLBS), oferind fundamentul logicii FPGA.Aceste blocuri pot fi programate și reconfigurate pentru a satisface cerințele specifice de proiectare, sporind versatilitatea generală a dispozitivului.

• RAM: FPGA este echipat cu 32.768 biți de memorie RAM intern, oferind capacități de stocare și regăsire eficientă a datelor pentru sarcini care implică manipularea datelor și stocarea temporară a datelor.

• Pinii I/O.: Cu 92 PIN-uri I/O, XC2S50-5TQG144I asigură conectivitate externă amplă, permițându-i să interfațăm cu alte dispozitive și componente dintr-un sistem pentru integrarea cuprinzătoare a sistemului.

• Tensiune de funcționare: Dispozitivul funcționează la o tensiune nominală de 2,5V, cu un interval acceptabil de la 2.375V la 2.625V.Această gamă de tensiune ajută la asigurarea funcționării stabile și a performanței fiabile în diferite condiții electrice.

• Interval de temperatură: XC2S50-5TQG144I este proiectat să funcționeze eficient într -o gamă largă de temperatură, de la -40 ° C până la +100 ° C, ceea ce îl face potrivit pentru implementarea în medii cu condiții termice provocatoare.

XC2S50-5TQG144I Diagrama blocului

Diagrama arată cum semnalele se deplasează și iese din XC2S50-5TQG144I FPGA.Acesta explică modul în care cip -ul gestionează semnalele de intrare și ieșire pentru a comunica cu alte componente.Pe Partea de ieșire , semnalele vin din interiorul FPGA și parcurg unități de depozitare numite Flip-Flops.Aceste flip-flops dețin date și se asigură că semnalele se schimbă la momentul potrivit.Semnalele trec apoi printr -un tampon de ieșire programabil, care ajustează cât de puternic este semnalul și controlează cât de rapid se schimbă.Există, de asemenea, un comutator (control OE) care decide dacă ieșirea ar trebui să fie activă sau să rămână oprită.Un circuit de protecție previne deteriorarea de la energia electrică statică înainte ca semnalul să ajungă la pinii I/O, care se conectează la alte dispozitive.Pe Partea de intrare, semnale din exterior intră prin bufferul de intrare programabil, care le procesează înainte de a le trimite în FPGA.O unitate de întârziere programabilă ajută la reglarea calendarului semnalului, astfel încât totul să rămână în sincronizare.FPGA poate utiliza, de asemenea, o tensiune de referință internă (VREF) pentru a se potrivi cu diferite niveluri de tensiune, ceea ce face mai ușor să funcționeze cu diferite tipuri de circuite.Unii pini I/O împărtășesc această referință de tensiune pentru a menține semnalele stabile.Acest design ajută FPGA să gestioneze eficient semnalele, asigurând o sincronizare, protecție și compatibilitate adecvată cu diferite componente electronice.

Specificații XC2S50-5TQG144I

|

Tip |

Parametru |

|

Producător |

Amd xilinx |

|

Serie |

Spartan®-II |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Numărul de laboratoare/CLBS |

384 |

|

Numărul de elemente/celule logice |

1728 |

|

Biți de ram totale |

32.768 |

|

Numărul de I/O. |

92 |

|

Numărul de porți |

50.000 |

|

Tensiune - alimentare |

2.375V ~ 2.625V |

|

Tip de montare |

Montare la suprafață |

|

Temperatura de funcționare |

-40 ° C ~ 100 ° C (TJ) |

|

Pachet / carcasă |

144-LQFP |

|

Pachet de dispozitive furnizor |

144-TQFP (20x20) |

|

Numărul produsului de bază |

XC2S50 |

Aplicații XC2S50-5TQG144I

Sisteme încorporate

În sistemele încorporate, XC2S50-5TQG144I oferă logica necesară pentru aplicațiile bazate pe microcontroller.Este utilizat pe scară largă în electronice auto, dispozitive portabile și robotice la scară mică pentru a spori funcționalitatea și receptivitatea.

Prelucrarea semnalului

FPGA excelează în sarcinile de procesare a semnalului, unde este necesară capacitatea sa de a efectua procesarea paralelă.Este ideal pentru procesarea audio și video, telecomunicații și analiza datelor, oferind puterea de putere pentru a gestiona algoritmi complexi și fluxuri de date de mare viteză.

Sisteme de control industrial

Sistemele de control industrial beneficiază de robustetea și programabilitatea acestui FPGA, ceea ce îl face potrivit pentru aplicații precum controlul procesului, automatizarea mașinilor și monitorizarea sistemului.Fiabilitatea sa asigură o performanță constantă în medii care necesită precizie și stabilitate operațională.

Sisteme de comunicare

În sistemele de comunicare, XC2S50-5TQG144I ajută la gestionarea transmiterii și recepției datelor, de a susține activități, cum ar fi modularea semnalului și demodularea, conversia protocolului și rutarea rețelei.Adaptabilitatea sa este esențială în evoluția infrastructurilor de telecomunicații și a tehnologiilor wireless emergente.

Prototiparea și dezvoltarea

FPGA este, de asemenea, utilizat pe scară largă pentru prototiparea circuitelor digitale.Mulți îl folosesc pentru a -și testa și perfecționa ideile înainte de producția finală, în special în proiecte complexe de proiectare a cipurilor ASIC și personalizate.Această capacitate reduce timpul și costurile de dezvoltare, accelerând calea de la concept la piață.

XC2S50-5TQG144i Piese similare

Avantaje XC2S50-5TQG144I

Eficiența costurilor

XC2S50-5TQG144I se remarcă pentru accesibilitatea sa, oferind mai multe funcții pe dolar decât multe FPGA-uri concurente.Această rentabilitate este obținută printr-o tehnologie avansată de proces și o arhitectură eficientă, permițând o implementare mai largă pe piețele sensibile la costuri.

I/O de înaltă performanță și ambalaje

Acest FPGA acceptă o gamă largă de standarde I/O și este disponibil în diferite opțiuni de ambalare rentabile.Aceste caracteristici asigură că dispozitivul poate fi integrat în mai multe aplicații fără a sacrifica performanța, ceea ce îl face ideal atât pentru piețele de înaltă calitate, cât și pentru cele conduse de volum, unde versatilitatea interfeței și constrângerile fizice sunt factori.

Caracteristici la nivel de sistem

Echipat cu funcții avansate de gestionare a memoriei, cum ar fi RAM distribuite și RAM de bloc configurabil, XC2S50-5TQG144I îmbunătățește eficiența de gestionare a datelor.Aceste caracteristici facilitează sarcini complexe de stocare și procesare a datelor, stimulând performanța și scalabilitatea generală a sistemului.

Reprogramabilitate

Reprogramabilitatea XC2S50-5TQG144I permite modificări nelimitate ale configurației sale, ceea ce este benefic în faza de dezvoltare.Această flexibilitate permite rafinarea proiectelor prin actualizări iterative fără costuri hardware suplimentare, favorizând inovația și reducând timpul la produsul final.

Pași de programare XC2S50-5TQG144I

Programarea FPGA XC2S50-5TQG144I din seria Spartan-II a AMD Xilinx implică o serie structurată de pași concepute pentru a traduce eficient un design digital într-o configurație FPGA funcțională.Iată un ghid integrat și detaliat pentru a vă ajuta prin procesul de programare:

1. Intrare de proiectare

Începeți cu faza de intrare de proiectare, unde vă creați logica digitală folosind un limbaj de descriere hardware (HDL), cum ar fi VHDL sau Verilog.Acest pas inițial implică detalierea funcționalității și logicii pe care doriți să o implementați în FPGA.Este necesar ca proiectarea dvs. să fie precisă și să reprezinte cu exactitate operațiunile prevăzute pentru a asigura sinteza și implementarea cu succes.

2. Sinteză

În etapa de sinteză, utilizați un instrument de sinteză pentru a converti codul dvs. HDL într -o listă de net.O listă net este o defalcare a designului dvs. într-un format care include diverse elemente logice interconectate, cum ar fi porțile și flip-flops.Acest proces traduce designul teoretic dvs. într -un plan practic pe care FPGA îl poate înțelege și implementa.

3. Implementare

Implementarea implică mai multe sub-trepte: mapare, plasare și rutare.Maparea atribuie elementele listei de net la blocuri logice specifice din FPGA.Plasarea determină locațiile fizice ale acestor blocuri de pe cipul FPGA pentru a optimiza performanța și utilizarea resurselor.Rutarea conectează aceste blocuri prin resursele de interconectare programabile ale FPGA.Această fază asigură că proiectarea îndeplinește toate constrângerile fizice și de performanță.

4. Definiție de constrângere

În timpul procesului de proiectare, este necesară definirea constrângerilor.Constrângerile Ghid instrumentele de implementare prin specificarea cerințelor, cum ar fi calendarul (cât de rapid ar trebui să funcționeze FPGA) și alocări de pin (care pini de pe FPGA se vor conecta la diferite părți ale hardware -ului dvs.).Acestea sunt articulate într-un fișier de constrângeri ale utilizatorului (UCF), care ajută la reglarea fină a proiectării pentru a îndeplini standardele operaționale specifice.

5. Generarea bitstream

Odată ce proiectarea dvs. trece cu succes prin faza de implementare, următorul pas este să generați un fișier bitstream.Acest fișier conține toate datele de configurare necesare FPGA pentru a executa proiectarea.Bitstream -ul este ieșirea finală a procesului de programare, reprezentând starea completă, programată a FPGA.

6. Programarea dispozitivului

Ultimul pas este să încărcați bitstream-ul în FPGA XC2S50-5TQG144I, care se poate face folosind diferite moduri de configurare în funcție de configurarea dvs.În Modul de serie Master, FPGA citește în mod autonom datele de configurare dintr-un PROM în serie atașat (memorie programabilă pentru citire numai). Mod de serie sclav Permite unui dispozitiv principal extern, cum ar fi un microcontroller, să alimenteze datele de configurare FPGA în serie. Mod paralel sclav Permite programarea de mare viteză furnizând date de configurare în paralel de pe un dispozitiv principal extern.În sfârșit, Mod de scanare de graniță (JTAG) Utilizează interfața JTAG atât pentru programare, cât și pentru testare, ceea ce o face utilă în timpul dezvoltării pentru depanarea și verificarea iterativă.

XC2S50-5TQG144I Dimensiuni de ambalare

XC2S50-5TQG144I este un tablou de poartă programabilă de câmp (FPGA) din familia Spartan-II a lui Xilinx, adăpostită într-un Pachet de 144 pini subțiri quad pachet (TQFP).Acest pachet măsoară 20 mm x 20 mm.

XC2S50-5TQG144I Producător

XC2S50-5TQG144I este un FPGA din familia Spartan-II, fabricat de AMD Xilinx.Xilinx, acum parte din Amd, este o companie de margine de semiconductor specializată în FPGA, SOC -uri adaptive și alte dispozitive logice programabile.XC2S50-5TQG144I a fost inițial dezvoltat în seria Xilinx Spartan-II, oferind 50.000 de porți de sistem și 1.728 de celule logice, concepute pentru aplicații de înaltă performanță, dar rentabile.Cu achiziția lui Xilinx de către AMD, compania continuă să sprijine produse vechi precum seria Spartan-II, avansând în același timp arhitecturi FPGA mai noi.Cu toate acestea, XC2S50-5TQG144I este un FPGA de generație mai veche și se poate confrunta cu eventualele obsolescență, deoarece schimbările AMD Xilinx se concentrează către familii FPGA mai avansate.

Concluzie

XC2S50-5TQG144I FPGA este un cip rentabil și reprogramabil, care oferă performanțe și flexibilitate deosebite.Este utilizat pe scară largă în sisteme încorporate, mașini industriale și rețele de comunicații, datorită procesării sale de mare viteză și a opțiunilor puternice de conectare.Cu capacitatea sa de a fi programat și actualizat, acest FPGA ajută la testarea și dezvoltarea ideilor noi înainte de producția finală.Deși sunt disponibile FPGA mai noi, acest model rămâne o alegere solidă pentru proiectele care au nevoie de o soluție FPGA fiabilă și accesibilă.Acest ghid oferă o imagine de ansamblu clară și simplă a caracteristicilor, utilizărilor și proceselor de programare ale FPGA, ceea ce îl face o resursă valoroasă pentru toată lumea.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Pot folosi XC2S50-5TQG144I pentru aplicații de mare viteză?

XC2S50-5TQG144I acceptă viteze de până la 200 MHz, ceea ce o face potrivită pentru majoritatea aplicațiilor încorporate și industriale.Cu toate acestea, dacă proiectul dvs. necesită interfețe de mare viteză, cum ar fi memoria PCIe sau DDR, este posibil să aveți nevoie de un FPGA mai avansat, cum ar fi seria Spartan-6 sau Artix-7.

2. Cum se compară XC2S50-5TQG144i cu noul FPGA-uri Spartan-3 sau Spartan-6?

În timp ce FPGA mai noi, cum ar fi Spartan-3 sau Spartan-6, oferă performanțe îmbunătățite, densitate logică mai mare și caracteristici suplimentare, XC2S50-5TQG144I rămâne o alegere preferată pentru proiectele sensibile la costuri, cu o complexitate moderată.Dacă aveți nevoie de compatibilitate

3. Ce instrumente de programare sunt compatibile cu FPGA XC2S50-5TQG144I?

XC2S50-5TQG144I este programat folosind Xilinx ISE (Mediu software integrat).În timp ce instrumentele Xilinx mai noi, cum ar fi Vivado, nu acceptă familia Spartan-II, ISE oferă toate funcționalitățile de proiectare, sinteză și programare necesare pentru acest FPGA.

4. Pot migra un design Spartan-II existent către un FPGA mai nou?

Da, dar necesită modificări.Noile familii Spartan-3 și Spartan-6 folosesc diferite arhitecturi, niveluri de tensiune și metode de configurare.Dacă aveți în vedere migrația, vă putem ajuta la selectarea alternativelor adecvate și la minimizarea modificărilor de proiectare.

5. Suporta XC2S50-5TQG144I Programarea JTAG?

R: Da, FPGA acceptă programarea de scanare a graniței JTAG (IEEE 1149.1), care permite depanarea și configurația ușoară folosind o interfață JTAG standard.Acest lucru este util atât pentru programarea inițială, cât și pentru reconfigurarea fără memorie externă.

XC4013XL-3PQ240C FPGA: alternative, specificații, aplicații și fișă de date

pe 2025/03/18

Amplificatoare de putere RF: Cum funcționează, care este mai eficient

pe 2025/03/18

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147770

-

Pinut și caracteristici USB-C

pe 2000/04/18 112006

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111351

-

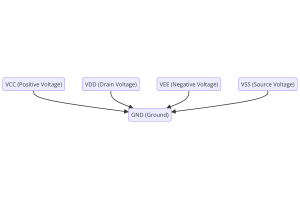

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83768

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79564

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66959

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63098

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63040

-

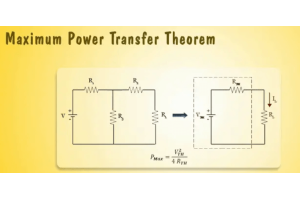

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54096

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52184