EP2S60F672C4 FPGA: Caracteristici, aplicații, programare și fișă de date

În acest ghid, veți obține o imagine de ansamblu clară a EP2S60F672C4, un FPGA puternic din familia Intel Stratix II.Veți afla despre principalele sale caracteristici, arhitectură, structură de bloc și specificații tehnice pentru a înțelege cum se încadrează în proiecte digitale avansate.De asemenea, vă parcurge pașii de programare, aplicațiile, avantajele și dezavantajele sale, astfel încât să puteți vedea exact unde și cum poate fi utilizat acest dispozitiv.Catalog

Ce este EP2S60F672C4?

EP2S60F672C4 este un FPGA de înaltă densitate de la Intel (fostul Altera), aparținând familiei Stratix II.Construit pe un proces SRAM de cupru de 90 nm, 1,2 V, oferă o capacitate de logică substanțială într-un pachet FBGA de 672 cu bile, ceea ce îl face ideal pentru sisteme digitale complexe.Ca parte a seriei EP2S, dispozitivul „60” se află în gama de la mijlocul-superior al liniei Stratix II, oferind un echilibru puternic de densitate logică, memorie încorporată și resurse I/O.Cunoscut pentru arhitectura și fiabilitatea robustă, acest FPGA rămâne o alegere de încredere în multe proiecte avansate.

Căutați EP2S60F672C4?Contactați -ne pentru a verifica stocul curent, timpul de plumb și prețurile.

EP2S60F672C4 Modele CAD

Simbol EP2S60F672C4

EP2S60F672C4 Amprentă

EP2S60F672C4 Model 3D

Caracteristici EP2S60F672C4

• Proces avansat de 90 nm, 1,2 V CMOS

EP2S60F672C4 este fabricat pe un proces CMOS de cupru de 90 nm pentru toate straturile care rulează la o tensiune de bază de 1,2 V.Această tehnologie permite un consum de putere redus, și o densitate logică mai mare în comparație cu generațiile FPGA mai vechi.

• Arhitectura modulului logic adaptiv (ALM)

Dispozitivul folosește ALM -uri ca bloc de construcții logice în loc de elemente logice tradiționale.Această arhitectură îmbunătățește utilizarea resurselor, permițând implementarea eficientă a funcțiilor logice mai complexe în aceeași zonă de siliciu.

• Densitate logică ridicată

Cu aproximativ 60.440 de elemente logice (24.176 pomană), FPGA acceptă modele digitale mari și sofisticate.Această capacitate ridicată o face potrivită pentru aplicații precum procesarea semnalului, comunicații și sisteme de control încorporate.

• Memorie On-Chip Trimatrix ™

EP2S60F672C4 integrează trei tipuri de blocuri RAM, (M512, M4K și M-RAM) pentru a oferi un total de aproximativ 2,4 mbits de memorie încorporată.Acest amestec permite implementarea în mod eficient FIFO-uri mici, tampoane medii și amintiri mari cu port dual.

• Blocuri DSP dedicate

Dispozitivul include 36 de blocuri DSP dedicate proiectate pentru operații aritmetice, cum ar fi multiplicațiile, acumulările și filtrarea FIR.Aceste blocuri stimulează performanța în sarcinile cu intensitate de calcul în timp ce economisesc resurse logice generale.

• I/O de mare viteză și integritatea semnalului

Suportă diverse standarde de I/O unidin și diferențiale, împreună cu circuitele de aliniere dinamică a fazelor (DPA).Aceste caracteristici permit transferul de date stabil, de mare viteză, până la 1 Gbps, asigurând o comunicare fiabilă cu componentele externe.

• Suport de interfață de memorie externă bogată

FPGA este compatibil cu DDR, DDR2, QDR II, RLDRAM II și alte standarde de memorie.Suportul de interfață încorporat simplifică proiectarea plăcii și obține un randament ridicat de date pentru aplicații intensive în memorie.

• Gestionarea flexibilă a ceasului

Până la 12 PLL-uri pe cip permit înmulțirea ceasului, diviziunea, schimbarea fazelor și comutarea fără glitch.Puteți regla domenii de ceas și reduceți bruiajul, susținând frecvențele de ceas interne de până la 500-550 MHz.

• Criptare și reconfigurare bitstream

EP2S60F672C4 acceptă criptarea Bitstream bazată pe AES pentru a asigura proprietatea intelectuală.De asemenea, oferă capacitate de reconfigurare la distanță, permițând actualizări pe teren fără a înlocui dispozitivul.

Diagrama blocului Stratix II

Diagrama blocului Stratix II, așa cum se arată pentru EP2S60F672C4, ilustrează aranjamentul intern al resurselor logice, memoriei și DSP care formează nucleul FPGA.Blocurile de matrice logice (laboratoare) sunt aranjate într-o grilă obișnuită, înconjurate de coloane RAM și DSP încorporate, care asigură capacități de stocare aritmetică rapidă și de stocare pe cip.Elementele de I/O periferice și rețelele de ceasuri încadrează această structură, permițând transferul de date eficient și controlul de calendar între FPGA și dispozitivele externe.Această diagramă este importantă, deoarece ajută la înțelegerea modului în care sunt organizate diferite blocuri funcționale, permițându -le să optimizeze plasarea, rutarea și performanța generală a sistemului.

Diagrama Băncilor Stratix II I/O

Această diagramă Stratix II I/O Banks ilustrează modul în care sunt grupate pinii de intrare/ieșire ale EP2S60F672C4 și ce standarde electrice acceptă fiecare grup.Fiecare bancă I/O este proiectată pentru a gestiona niveluri specifice de tensiune, tipuri de semnalizare și funcții precum LVTTL, SSTL, LVDS sau standarde de intrare a ceasului.Aspectul arată modul în care diferite bănci (de exemplu, 1, 2, 5, 6 vs. 3, 4, 7, 8, etc.) sunt optimizate fie pentru I/O sau pentru semnalizare diferențială de mare viteză, inclusiv pentru suportul pentru intrările de ceas LVDS/LVPECL la margini.Înțelegerea acestei structuri este importantă atunci când alocați pini, deoarece o selecție bancară adecvată asigură compatibilitatea electrică, simplifică rutarea plăcii și maximizează performanța FPGA în proiectele de mare viteză.

Specificații EP2S60F672C4

|

Tip |

Parametru |

|

Producător |

Alterra/Intel |

|

Serie |

Stratix® II |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Numărul de laboratoare/CLBS |

3022 |

|

Numărul de elemente/celule logice |

60.440 |

|

Biți de ram totale |

2.544.192 |

|

Numărul de I/O. |

492 |

|

Tensiune - alimentare |

1,15 V ~ 1,25 V |

|

Tip de montare |

Montare la suprafață |

|

Temperatura de funcționare |

0 ° C ~ 85 ° C (TJ) |

|

Pachet / carcasă |

672-bbga |

|

Pachet de dispozitive furnizor |

672-FBGA (27 × 27) |

|

Numărul produsului de bază |

EP2S60 |

Aplicații EP2S60F672C4

1.. Procesare digitală a semnalului (DSP) și filtrare

EP2S60F672C4 este potrivit pentru implementarea funcțiilor DSP de înaltă performanță, cum ar fi filtrele FIR și IIR, procesarea FFT și operațiuni aritmetice complexe.Blocurile sale DSP dedicate gestionează în mod eficient multiplicațiile și acumulările, eliberând resurse logice generale pentru alte sarcini.Memoria On-Chip Trimatrix ™ permite tamponarea și conducta de date lină, ceea ce este excelent pentru procesarea în timp real la rate mari de eșantion.Acest lucru face ca dispozitivul ideal pentru aplicații avansate de semnal audio, video și radar.

2. Comunicare de mare viteză și rețea

Interfețele I/O de mare viteză ale FPGA și alinierea în fază dinamică (DPA) acceptă transmisia de date fiabilă, la nivel de gigabit.Poate implementa protocoale de comunicare și funcții de strat fizic pentru sisteme precum routere, comutatoare și interconectări de plan de back -plan.Cu capacitatea sa logică mare și PLL-urile flexibile, poate gestiona conversii complexe de sincronizare și protocol între mai multe interfețe de mare viteză.Aceste capacități îl fac o potrivire puternică pentru infrastructura de telecomunicații și echipamentele de rețea cu lățime mare de bandă.

3. Controlere de memorie și sisteme de prelucrare a datelor

EP2S60F672C4 acceptă diverse interfețe de memorie externe, inclusiv DDR, DDR2, RLDRAM II și QDR II, ceea ce îl face ideal pentru proiectarea controlerelor de memorie cu lățime de bandă mare.Poate gestiona tamponarea datelor, generarea de adrese și arbitrajul la viteze mari, cu latență minimă.Combinația de rețele de ceas rapid și blocuri RAM încorporate permite gestionarea eficientă a fluxurilor de date mari.Acest lucru face ca FPGA să fie potrivit pentru procesarea imaginilor, streamingul video și platformele de calcul științific care se bazează pe randamentul de date grele.

4. Logica personalizată și accelerația încorporată

Cu peste 60.000 de elemente logice și un management bogat de ceasuri, FPGA poate găzdui acceleratoare hardware personalizate pentru algoritmi specifici.Designerii îl folosesc adesea pentru a descărca sarcini intensive din punct de vedere calculat din procesoare, cum ar fi criptarea, analizarea protocolului sau buclele de control în timp real.De asemenea, poate integra mai multe blocuri funcționale, ceea ce îl face adecvat pentru modele complexe asemănătoare cu SOC.Această flexibilitate o face valoroasă în aplicații precum automatizarea industrială, sistemele de securitate și unitățile de control aerospațial.

5. Platforme de prototipare și dezvoltare educațională

Dispozitivul EP2S60 se găsește în mod obișnuit pe kiturile de dezvoltare FPGA utilizate pentru prototipare, testare și cercetare academică.Echilibrul său de capacitate logică, număr de I/O și DSP permite inginerilor și studenților să implementeze și să verifice sisteme complete pe un singur cip.Suportă iterația rapidă a proiectelor digitale, permițând verificarea hardware înainte de a se angaja la dezvoltarea ASIC.Multe universități și laboratoare de cercetare și dezvoltare îl folosesc pentru a învăța concepte avansate de proiectare digitală și procesare a semnalului.

EP2S60F672C4 Piese similare

|

Specificații |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Familie / serie |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Elemente logice (LE) |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

60.440 |

|

Pomană |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

24.176 |

|

Pachet |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Grad de viteză |

C4 (STD) |

C3 (mai rapid) |

C5 (mai rapid) |

C5 (mai rapid) |

I4 (std) |

I3 (mai rapid) |

|

Grad de temperatură |

Comercial (0 ~ 70 ° C) |

Comercial |

Comercial |

Comercial |

Industrial (−40 ~ 100 ° C) |

Industrial (−40 ~ 100 ° C) |

|

Pinii I/O. |

492 |

492 |

492 |

492 |

492 |

492 |

|

Memorie pe cip |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

|

Tensiune de bază |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

1.2 V. |

|

Diferența cheie |

Viteza comercială de bază |

Coșul de viteză C3, „N” fără plumb |

Coș de viteză mai mare |

Coș de viteză mai mare, varianta „n” |

Temperatură industrială, aceeași densitate |

Viteză industrială, mai rapidă, fără plumb |

EP2S60F672C4 Pași de programare

Înainte de a putea utiliza EP2S60F672C4 FPGA în designul dvs., trebuie să îl configurați corect cu bitstream -ul compilat.Acest proces implică pregătirea fișierului de programare, configurarea interfeței hardware și asigurarea faptului că configurația se încarcă corect la pornire.

Pasul 1: Creați și compilați designul dvs.

Începeți prin dezvoltarea designului logic folosind software -ul Intel Quartus II.După finalizarea designului, îl compilam pentru a genera fișierul de programare (.SOF sau .POF) special pentru dispozitivul EP2S60F672C4.Procesul de compilare verifică momentul, alocările de pin și utilizarea resurselor pentru a vă asigura că proiectarea dvs. se încadrează în arhitectura FPGA.Odată compilat, bitstream -ul dvs. este gata pentru configurarea dispozitivului.

Pasul 2: Configurați hardware -ul de programare

În continuare, pregătiți interfața de programare fizică între computer și placa FPGA.De obicei, aceasta implică conectarea unui blaster USB sau a unui cablu JTAG compatibil la portul JTAG al dispozitivului.Ar trebui să verificați dacă Quartus II recunoaște programatorul și că dispozitivul țintă este detectat corect.Acest pas asigură o comunicare stabilă înainte de a iniția procesul de configurare.

Pasul 3: Încărcați fișierul de programare în dispozitiv

Folosind instrumentul Programator Quartus II, adăugați fișierul compilat .SOF sau .POF și selectați EP2S60F672C4 din lista de dispozitive detectate.Apoi inițiați secvența de programare, timp în care Bitstream este transferat și încărcat în celulele de configurare SRAM ale FPGA.Ar trebui să monitorizați bara de progres și mesajele de stare pentru a confirma o configurație de succes.Odată finalizat, FPGA începe să execute imediat logica programată.

Pasul 4: Verificați configurația și funcționarea

După programare, verificați dacă dispozitivul funcționează așa cum este prevăzut.Quartus II oferă o opțiune de verificare pentru a verifica semnalele CRC de configurare și starea, asigurându -se că proiectarea este încărcată corect.De asemenea, vă puteți testa funcțiile de I/O sau puteți rula o simulare funcțională pentru a confirma comportamentul sistemului.Acest pas final asigură că proiectarea dvs. este complet operațională și stabilă pe hardware.

EP2S60F672C4 Avantaje și dezavantaje

Avantaje

• Densitate logică ridicată pentru proiecte complexe

• Un raport bun performanță-cost

• Migrație ușoară în cadrul aceleiași familii

• Instrumente de dezvoltare stabile și mature

• Fiabilitate dovedită în uz industrial

Dezavantaje

• învechit și mai greu de sursă

• Consum de energie mai mare decât FPGA mai nou

• Fără transceiver moderni de mare viteză

• Închidere mai dificilă a timpului la o utilizare ridicată

• Scalabilitate limitată pentru protocoale viitoare

EP2S60F672C4 Dimensiuni de ambalare

|

Tip |

Parametru |

|

Tip de pachet |

672-FBGA (FINELINE BGA) |

|

Mărimea corpului (L × W) |

27,00 mm × 27,00 mm |

|

Înălțimea totală a pachetului (a) |

Max 3,50 mm |

|

Înălțimea standoff (A1) |

Min 0,30 mm |

|

Grosimea substratului (A2) |

Max 3,00 mm |

|

Diametrul bilei (B) |

0,50 mm - 0,70 mm |

|

Ball Pitch (E) |

1,00 mm |

|

Numărul de mingi |

672 |

|

Stil de montare |

Montare la suprafață |

|

Descrierea pachetului |

FBGA, rețea 27 × 27 mm |

EP2S60F672C4 Producător

EP2S60F672C4 FPGA este fabricat de Altera Corporation, un pionier principal în dispozitivele logice programabile.În 2015, Altera a fost achiziționată de Intel, iar produsul se încadrează acum sub Grupul de soluții programabile Intel (PSG), care continuă să sprijine și să furnizeze familiile FPGA consacrate ale ALTERA.Intel menține linia Stratix II ca parte a portofoliului său de produse moștenite, asigurând documentația, suportul pentru instrumente și disponibilitatea pe termen lung pentru aplicații industriale și de comunicare.

Concluzie

EP2S60F672C4 combină densitate logică ridicată, arhitectură de memorie flexibilă și caracteristici I/O robuste pentru a sprijini sisteme digitale complexe.Proiectarea sa bazată pe ALM, memoria Trimatrix ™, blocurile DSP și caracteristicile de gestionare a ceasurilor permit implementarea eficientă a aplicațiilor solicitante.Deși oferă fiabilitate dovedită și sprijin de dezvoltare matur, se confruntă cu limitări precum obsolescența și lipsa transceiverilor moderni în comparație cu generațiile FPGA mai noi.În general, performanța sa echilibrată și versatilitatea îl fac o alegere solidă pentru procesarea semnalului, comunicarea, manipularea datelor și aplicațiile de prototipare.

Fișă de date pdf

Fisa de date EP2S60F672C4:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Poate funcționa EP2S60F672C4 cu interfețe de memorie DDR moderne?

Da, acceptă interfețele DDR, DDR2, QDR II și RLDRAM II, care acoperă multe standarde comune de memorie externă.Acest lucru îl face potrivit pentru aplicații de prelucrare a datelor cu lățime mare de bandă.

2. EP2S60F672C4 necesită o manipulare sau depozitare specială?

Da, la fel ca și alte componente ambalate BGA, ar trebui să fie păstrată în ambalaje controlate de umiditate și gestionate cu protecție ESD.În urma practicilor de stocare adecvate ajută la menținerea lipiturii și a fiabilității dispozitivului în timpul asamblării.

3. Cum puteți reduce consumul de energie în proiectele EP2S60F672C4?

Puteți optimiza utilizarea logică, ceasurile neutilizate de poartă, tensiunile de I/O mai mici, acolo unde este posibil, și folosiți opțiuni de sinteză conștiente de putere în Quartus II pentru a reduce la minimum traseul general al puterii.

4. Ce instrumente de programare sunt necesare pentru EP2S60F672C4?

Veți avea nevoie de software Intel Quartus II pentru proiectare, compilare și programare, împreună cu un blaster USB sau un cablu JTAG compatibil pentru a configura dispozitivul.

5. EP2S60F672C4 acceptă actualizări pe teren sau reconfigurare la distanță?

Da, acceptă criptarea bitstream bazată pe AES și reconfigurarea la distanță, permițându-vă să vă actualizați sistemul în siguranță fără a înlocui fizic FPGA.

Totul despre LFXP6C-3FN256C Semiconductor cu zăbrele

pe 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, Caracteristici, Programare și Ghid de fișă de date

pe 2025/10/3

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147778

-

Pinut și caracteristici USB-C

pe 2000/04/18 112035

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111352

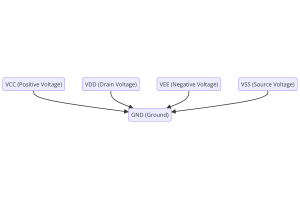

-

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83793

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79602

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66976

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63111

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63044

-

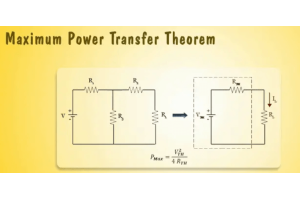

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54097

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52198