XC2C256-7TQ144C CPLD: PINOUT, Caracteristici, Programare și Ghid de fișă de date

În acest ghid, veți arunca o privire clară asupra XC2C256-7TQ144C, un CPLD cu putere redusă din familia Coolrunner-II de la Xilinx (acum AMD).Veți afla despre configurația PIN, modelele CAD și caracteristicile principale, cum ar fi capacitatea logică, opțiunile de I/O, suportul de tensiune și funcțiile de economisire a puterii.De asemenea, vom parcurge arhitectura, curba I/V și specificațiile sale, urmate de aplicații, piese similare, pași de programare, avantaje și dezavantaje, detalii despre ambalaje și informații despre producător, astfel încât să puteți înțelege exact modul în care acest dispozitiv se încadrează în proiectele dvs.Catalog

Ce este XC2C256-7TQ144C?

XC2C256-7TQ144C este un CPLD cu putere redusă (dispozitiv logic programabil complex) din familia Coolrunner-II a Xilinx, acum parte a AMD.Dispune de 256 macroceluri și vine într-un pachet TQFP de 144 de pini, conceput pentru o operație rapidă și deterministă, cu un consum de energie minimă.Funcționând pe un nucleu de 1,8 V, oferă performanțe fiabile într-un factor de formă compactă și este potrivit pentru proiectele care necesită capacitate instantanee și implementare logică eficientă.Ca parte a serialului versatil Coolrunner-II, beneficiază de o arhitectură dovedită și o compatibilitate largă a designului.

Căutați XC2C256-7TQ144C?Contactați -ne pentru a verifica stocul curent, timpul de plumb și prețurile.

XC2C256-7TQ144C Diagrama de pin-out

Diagrama de pin-out XC2C256-7TQ144C arată cum sunt aranjate cele 144 de pini pentru funcții de I/O de putere, sol, JTAG și utilizator.Majoritatea pinilor sunt I/O, care pot fi configurate ca intrări sau ieșiri și sunt distribuite uniform pentru a suporta rutarea flexibilă.Pinurile VCC, VCCIO1, VCCIO2, VAUX și GND sunt plasate în jurul pachetului pentru a oferi o distribuție stabilă de putere și mai multe opțiuni de tensiune I/O.Pinii JTAG (TDI, TDO, TMS, TCK) sunt grupate pentru o programare și testare ușoară în sistem.

Modele CAD XC2C256-7TQ144C

Simbol XC2C256-7TQ144C

XC2C256-7TQ144C Amprentă

XC2C256-7TQ144C Model 3D

Caracteristici XC2C256-7TQ144C

• Tipul dispozitivului și familia

XC2C256-7TQ144C este un dispozitiv logic programabil complex (CPLD) care aparține familiei Coolrunner-II dezvoltate de Xilinx (acum AMD).Este conceput pentru consumul redus de energie, menținând în același timp performanțe logice rapide și deterministe, ceea ce îl face ideal pentru logica de control și aplicațiile de interfațare.

• Capacitate logică

Acest dispozitiv conține 256 de macroceluri, care sunt resursele logice programabile din CPLD.Aceste macroceluri pot fi configurate pentru a implementa diverse funcții logice combinaționale și secvențiale, oferind o capacitate moderată de control, logică de lipici și interfețe de bus.

• Blocuri logice (blocuri funcționale)

Integrează 16 blocuri de funcții care organizează și gestionează grupuri de macroceluri.Fiecare bloc oferă resurse locale de interconectare și pe termen lung, permițând implementarea logică flexibilă și o rutare eficientă în cadrul dispozitivului.

• PIN -uri I/O de utilizator

XC2C256-7TQ144C oferă până la 118 pini de I/O configurabili utilizatori în pachetul său TQFP-144.Acest număr ridicat de pini permite dispozitivului să interfațăm cu mai multe subsisteme simultan, ceea ce îl face potrivit pentru proiectele complexe la nivel de bord.

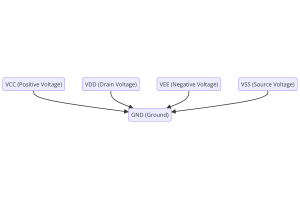

• Tensiune de bază (VCC)

Nucleul funcționează la un nivel nominal de 1,8 V (1,7 V până la 1,9 V), ceea ce ajută la reducerea consumului de energie în comparație cu CPLD -urile de 5 V mai vechi.Această tensiune mai mică este utilă în sistemele digitale moderne de tensiune mixtă.

• Suport I/O multi-tensiune

Băncile I/O acceptă mai multe standarde de tensiune, inclusiv 1,5 V, 1,8 V, 2,5 V și 3,3 V. Această flexibilitate permite CPLD să se interpună direct cu componentele care funcționează la diferite niveluri de tensiune fără schimbătoare de nivel extern.

• Funcționare de mare viteză

Cu o întârziere tipică de propagare pin-to-pin de aproximativ 5,7 ns (gradul de viteză „-7”), dispozitivul oferă o performanță rapidă și deterministă.Acest lucru îl face potrivit pentru aplicații critice de sincronizare, cum ar fi decodarea adreselor, arbitrajul autobuzului și controlul.

• Consum redus de energie

Seria Coolrunner-II este cunoscută pentru curenți de așteptare extrem de scăzute, adesea în gama de microamp.Această putere statică scăzută, combinată cu caracteristici dinamice de economisire a puterii, permite utilizarea eficientă a XC2C256-7TQ144C în sisteme alimentate de baterie sau mereu.

• Tehnologia Datagate

Această caracteristică permite să oprească intrările neutilizate, prevenind comutarea inutilă și reducerea consumului dinamic de energie.Este valoros în aplicațiile în care anumite semnale sunt inactive pentru perioade lungi.

• Programare JTAG în sistem

Dispozitivul acceptă IEEE 1149.1 (JTAG) și IEEE 1532 pentru programare în sistem.Aceasta înseamnă că CPLD poate fi configurat, testat și reprogramat fără a -l scoate de pe placă, simplificând dezvoltarea și actualizările.

• Structura de ceas avansată

XC2C256-7TQ144C include mai multe ceasuri globale, divizoare de ceas și registre declanșate cu două edge.De asemenea, oferă set/resetare globală și ceas local pe macrocell, oferind un control flexibil asupra sincronizării și sincronizării.

• Intrări Schmitt-Trigger

Pinii de intrare selectați pot fi configurați ca declanșatoare Schmitt pentru a îmbunătăți imunitatea zgomotului.Acest lucru este util pentru gestionarea semnalelor de intrare lente sau zgomotoase fără a adăuga circuite de condiționare externe.

• Caracteristici de ieșire flexibile

Ieșirile acceptă funcționarea în trei state, controlul vitezei, configurațiile de reținere a autobuzelor, redactarea deschisă și extragerea opțională.Aceste opțiuni facilitează adaptarea CPLD la diverse standarde de autobuz și condiții de încărcare externă.

• Matricea avansată de interconectare (AIM)

O matrice avansată de interconectare leagă eficient blocurile de funcții, oferind o rutare completă a produsului pe termen între dispozitiv.Acest lucru îmbunătățește flexibilitatea logică a plasării și ajută la menținerea performanței previzibile de sincronizare.

Arhitectură CPLD Coolrunner-II

Arhitectura CPLD Coolrunner-II a XC2C256-7TQ144C este construită în jurul blocurilor de funcții, blocurilor I/O și o matrice avansată de interconectare (AIM).Fiecare bloc de funcții conține macroceluri și un tablou logic programabil (PLA) care implementează logica definită de utilizator, în timp ce obiectivul tratează eficient semnalele între blocuri.Blocurile I/O interfață logica internă cu pini externi și JTAG dedicat JTAG și BSC/ISP Circuitry Support în programare și testare în sistem.Această arhitectură structurată și interconectată permite o performanță rapidă, deterministă, cu un consum redus de energie, ceea ce o face ideală pentru control, interfață și logică de lipici în sistemele digitale.

Curba tipică de I/V pentru XC2C256

Curba tipică de I/V pentru XC2C256-7TQ144C ilustrează relația dintre tensiunea de ieșire (VO) și curentul de ieșire (IO) pentru diferite tensiuni de alimentare I/O (1,5 V, 1,8 V, 2,5 V și 3,3 V).Pe măsură ce tensiunea de alimentare crește, dispozitivul poate sursa sau scufunda curenți mai mari înainte ca tensiunea de ieșire să înceapă să scadă semnificativ.Acest comportament este important pentru înțelegerea capacității de acționare a CPLD atunci când se interfață cu componentele externe, asigurând că nivelurile de semnal rămâne valabilă sub sarcină.Mulți folosesc această curbă pentru a selecta tensiuni de I/O adecvate și pentru a asigura o funcționare fiabilă în aplicațiile care necesită puncte forte de conducere a curentului specific.

Specificații XC2C256-7TQ144C

|

Tip |

Parametru |

|

Producător |

AMD/XILINX |

|

Serie |

Coolrunner II |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Tip programabil |

În sistem programabil |

|

Timp de întârziere TPD (1) Max |

6.7 ns |

|

Alimentare de tensiune - internă |

1,7 V ~ 1,9 V |

|

Numărul de elemente/blocuri logice |

16 |

|

Numărul de macroceluri |

256 |

|

Numărul de porți |

6000 |

|

Numărul de I/O. |

118 |

|

Temperatura de funcționare |

0 ° C ~ 70 ° C (TA) |

|

Tip de montare |

Montare la suprafață |

|

Pachet / carcasă |

144-LQFP

|

|

Pachet de dispozitive furnizor |

144-TQFP (20 × 20) |

|

Numărul produsului de bază |

XC2C256 |

Aplicații XC2C256-7TQ144C

1..

XC2C256-7TQ144C este ideal pentru implementarea logicii lipiciului, care conectează și coordonează semnalele între diferite componente digitale.Poate gestiona funcții precum decodarea adreselor, arbitrajul autobuzului și traducerea protocolului, permițând o comunicare lină între microcontrolere, memorie, senzori și alte periferice.Momentul său previzibil și întârzierile rapide de pin-pin asigură o interfață fiabilă chiar și în proiectele complexe ale plăcii.

2. Dispozitive cu putere redusă și cu baterii

Datorită tehnologiei sale Fast Zero Power (FZP) și curentului de așteptare foarte scăzut, acest CPLD este foarte potrivit pentru electronice portabile și cu baterii.Poate rămâne alimentat continuu în timp ce consumă energie minimă, ceea ce o face perfectă pentru circuitele de control sau monitorizare mereu.Puteți reduce utilizarea puterii în continuare cu caracteristici precum Datagate, ceea ce minimizează comutarea dinamică atunci când intrările sunt inactive.

3. Control logica și secvențarea

Dispozitivul excelează la implementarea mașinilor de stare finită, controlul sincronizării și secvențierea semnalului necesară în multe sisteme încorporate.Arhitectura sa deterministă, non-volatilă, permite logicii de control să devină activă imediat după pornire fără întârzieri de configurare.Acest lucru face o alegere puternică pentru resetarea logicii, a circuitelor de strângere de mână și a altor sarcini de control critic în timp.

4. Suportul sistemului încorporat și logica periferică

În proiectele încorporate, XC2C256-7TQ144C poate acționa ca un cip de asistență personalizabil, implementarea interfețelor specializate sau extinderea capacităților unui microcontroller.Poate gestiona protocoale de comunicare, cum ar fi SPI, I²C sau UART, să genereze selecții de cipuri sau să gestioneze rutele de întrerupere.Prin descărcarea acestor funcții de la CPU, simplifică dezvoltarea firmware -ului și îmbunătățește performanța generală a sistemului.

XC2C256-7TQ144C Piese similare

|

Specificații |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Familia de dispozitive |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

|

Densitatea logică (macroceluri) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Tip de pachet |

TQFP-144 |

TQFP-144 |

TQFP-144 (fără PB) |

VQFP-100 |

VQFP-100 (PB-Free) |

TQFP-144 |

|

Grad de viteză |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (mai rapid) |

|

Interval de temperatură |

Comercial (0 - 70 ° C) |

Industrial (-40-85 ° C) |

Industrial (-40-85 ° C) |

Comercial (0 - 70 ° C) |

Comercial (0 - 70 ° C) |

Comercial (0 - 70 ° C) |

|

Numărul de pini I/O. |

118 |

118 |

118 |

80 |

80 |

118 |

|

Tensiune de bază (VCC) |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

|

Suport de tensiune I/O. |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Conformitate / fără PB |

Standard |

Standard |

PB-Free / ROHS |

Standard |

PB-Free / ROHS |

Standard |

|

Diferențe |

Versiunea comercială de bază |

Versiune de temperatură industrială |

Versiune industrială + PB fără PB |

Pachet mai mic, mai puțini I/O |

Versiune mai mică fără PB |

Versiune de sincronizare mai rapidă |

XC2C256-7TQ144C Pași de programare

Programarea XC2C256-7TQ144C este un proces simplu care implică pregătirea proiectării dvs., generarea fișierului de programare și încărcarea acestuia în CPLD prin JTAG.Urmând cu atenție fiecare pas, puteți asigura o configurație de succes și o funcționare adecvată a dispozitivului pe placa dvs.

1. Proiectarea și sintetizarea

Începi prin a scrie designul logic folosind HDL (VHDL sau Verilog) sau intrare schematică.După finalizarea designului, rulați procesul de sinteză, care transformă logica dvs. în structura internă a dispozitivului de macroceluri și interconectări.Acest pas vă asigură că proiectarea dvs. este compatibilă cu arhitectura XC2C256 și gata de implementare.

2. Place și rute / implementare (montare)

În continuare, efectuați loc și ruta, cunoscute și sub denumirea de montare, care atribuie logica sintetizată la macroceluri fizice reale și resurse de rutare în CPLD.Instrumentul verifică constrângerile de sincronizare, rezolvă utilizarea resurselor și optimizează căile pentru a îndeplini performanța proiectării tale.Acest lucru asigură că circuitul va rula în mod fiabil odată programat în dispozitiv.

3. Generați fișier de programare

Odată ce implementarea este completă, generați fișierul de programare (bit, JAM sau format SVF) care conține datele de configurare exacte pentru dispozitiv.Acest fișier reprezintă modul în care fiecare macrocell, interconectare și I/O este configurată pentru a vă implementa logica.Pregătirea acestui fișier este necesară înainte de a trece la programarea reală a dispozitivului.

4. Programare JTAG / In-sistem

În cele din urmă, conectați dispozitivul la computer folosind un cablu de programare JTAG și deschideți instrumentul Xilinx Impact (sau echivalent).Apoi încărcați fișierul de programare generat și îl descărcați pe XC2C256-7TQ144C prin pinii JTAG (TDI, TDO, TCK, TMS).După finalizarea procesului, CPLD începe imediat să funcționeze cu logica programată, fără a necesita un ciclu de alimentare sau un memorie de configurare externă.

XC2C256-7TQ144C Avantaje și dezavantaje

Avantaje

• Putere de așteptare foarte scăzută, ideală pentru proiectele cu baterii.

• Funcționare instantanee fără întârziere de configurare.

• Momentul previzibil pentru închiderea mai ușoară a proiectării.

• Înlocuiește mai multe jetoane logice discrete, economisind spațiu și costuri.

• Suportă mai multe tensiuni de I/O fără schimbătoare de nivel extern.

Dezavantaje

• Capacitate logică limitată în comparație cu CPLD -uri mai mari sau FPGA.

• Fără transceiver DSP, RAM sau de mare viteză încorporate.

• Devenind învechit, ceea ce face mai greu aprovizionarea viitoare.

• Plafon de performanță mai mic pentru aplicații de mare viteză.

• Mai puțină flexibilitate de rutare pentru modele complexe sau neregulate.

XC2C256-7TQ144C Dimensiuni de ambalare

|

Tip |

Parametru |

|

Tip de pachet |

TQFP-144 |

|

Dimensiunea corpului pachetului |

20 mm × 20 mm |

|

Place Pitch |

0,5 mm |

|

Numărul de pini |

144 |

|

Înălțimea pachetului (max) |

1,4 mm |

|

Grosimea pachetului (nominal) |

1,0 mm |

|

Lungimea plumbului |

0,45 mm ~ 0,75 mm |

|

Lățimea plumbului |

0,17 mm ~ 0,27 mm |

|

Tip de montare |

Montare la suprafață |

|

Pachet de dispozitive furnizor |

144-TQFP (20 × 20) |

XC2C256-7TQ144C Producător

XC2C256-7TQ144C este fabricat de Xilinx, o companie lider în soluții logice programabile.Xilinx este recunoscut pe scară largă pentru tehnologiile de pionierat FPGA și CPLD, oferind dispozitive de încredere și de înaltă performanță pentru aplicații industriale, comerciale și de consum.Astăzi, Xilinx funcționează ca parte a Amd, continuând să furnizeze produse logice programabile avansate, cu sprijin puternic pe termen lung și inovație.

Concluzie

XC2C256-7TQ144C se remarcă pentru consumul său redus de energie, performanța deterministă rapidă și flexibilitatea I/O multi-tensiune, ceea ce îl face o alegere fiabilă pentru modelele digitale moderne.Combinația sa echilibrată de 256 de macroceluri, 118 pini I/O și arhitectură avansată de interconectare acceptă o gamă largă de funcții de control, interfațare și logică de lipici.Cu suport pentru programarea în sistem, caracteristici de economisire a puterii de date și configurații I/O robuste, se integrează fără probleme în sisteme încorporate și medii de tensiune mixtă.

Fișă de date pdf

Fișiere de date XC2C256-7TQ144C:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1.. XC2C256-7TQ144C necesită memorie de configurare externă?

Nu. Unul dintre avantajele sale este funcționarea instantanee.Configurația este stocată pe plan intern, astfel încât se prezintă gata să ruleze fără niciun fel de bal sau memorie flash externă.

2. Ce instrumente de programare sunt compatibile cu XC2C256-7TQ144C?

Puteți programa dispozitivul folosind software -ul Xilinx Impact cu un cablu de programare JTAG.Mulți folosesc, de asemenea, programatori JTAG terți compatibili, dar asigurați-vă că acceptă standardele IEEE 1149.1/1532.

3.. XC2C256-7TQ144C poate înlocui mai multe IC-uri logice discrete în designul dvs.?

Da.Cu cele 256 de macroceluri și I/O flexibile, acest CPLD poate integra mai multe funcții de logică și control de lipici într -un singur dispozitiv, ajutându -vă să reduceți spațiul de bord și numărul de componente.

4. Este XC2C256-7TQ144C adecvat pentru aplicații pentru baterii cu putere redusă?

Da.Datorită tehnologiei sale Fast Zero Power (FZP) și curentului de așteptare foarte scăzut, este ideal pentru circuite mereu, dispozitive portabile și sisteme încorporate sensibile la putere.

5. Puteți utiliza XC2C256-7TQ144C pentru procesarea semnalului de mare viteză?

Nu este conceput pentru sarcini DSP de mare viteză sau transceiver.Deși oferă întârzieri rapide de la pin-to-pin, este cel mai potrivit pentru logica de control, interfațare și sincronizare, nu pentru procesarea complexă a datelor.

EP2S60F672C4 FPGA: Caracteristici, aplicații, programare și fișă de date

pe 2025/10/4

EPM3256AFC256-7 Prezentare generală a CPLD: Caracteristici, Pinout, Programare și Aplicații

pe 2025/10/3

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147776

-

Pinut și caracteristici USB-C

pe 2000/04/18 112018

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111351

-

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83775

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79571

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66962

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63104

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63041

-

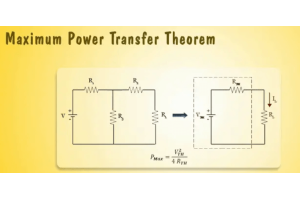

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54097

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52186