Evoluția și impactul arhitecturii RISC în calculul modern

Acest ghid explorează setul de instrucțiuni redus de calcul (RISC), o abordare cheie în proiectarea microprocesorului care crește viteza și eficiența prin simplificarea instrucțiunilor.Dezvoltat pentru prima dată în anii 1980, inspirat de conceptele anterioare ale MIPS Mainframe, RISC a arătat că utilizarea mai puține instrucțiuni ar putea îmbunătăți mult performanța.Condus de John Cocke la IBM, acest proiect a simplificat operațiuni de procesor pentru o execuție mai rapidă în comparație cu sistemele complexe.Astăzi, principiile RISC alimentează mulți microprocesoare moderne, conducând apăsarea pentru un calcul mai eficient.Articolul acoperă istoria RISC, ideile de bază, utilizările actuale și influența durabilă asupra tehnologiei.Catalog

Perspective îmbunătățite asupra arhitecturii computerului

Set de instrucțiuni reduse Calcularea (RISC) și setul de instrucțiuni complexe de calcul (CISC) reprezintă două abordări contrastante pentru arhitectura computerului, fiecare cu căi evolutive distincte.RISC's minimalist instruction set focuses on optimizing frequently used commands through efficient compiler strategies, enabling swift execution and reduced memory consumption, features that have made it a key player in high-performance systems like Compaq's Alpha, HP's PA-RISC, IBM's PowerPC, MIPS,și Sun's Sparc.În schimb, CISC se bazează pe modele hardware complexe pentru a obține câștiguri de performanță prin seturi de instrucțiuni mai complexe.Simplitatea RISC, consolidată de progresele tehnologiilor de memorie și executarea instrucțiunilor cu un singur ciclu, oferă o prelucrare rapidă și eficientă în medii cu cerere mare, unde este necesară o latență redusă.Inovațiile practice, cum ar fi controlul hardware rafinat și tehnicile de compilator sofisticate asigură că RISC rămâne relevant în gestionarea provocărilor moderne de calcul.În peisajul tehnologic cu evoluție rapidă de astăzi, eficiența de adaptare și procesare a RISC s-au dovedit în operațiunile intensive de date, oferind performanțe robuste de performanță a serverului și cicluri de dezvoltare agilă pentru a răspunde cerințelor crescânde ale calculului contemporan.Pe măsură ce arhitectura continuă să evolueze, amestecul RISC de simplitate și scalabilitate își consolidează semnificația de durată și potențialul transformator în diferite industrii.

Clasificarea în calculul modern

Conducte de instrucțiuni avansate și arta eficienței procesării

Arhitecturile RISC îmbrățișează un set de abordări sofisticate pentru a crește eficiența calculațională, abordând astfel subtil dorința înnăscută de viteză și reacție.Folosind conducte de instrucțiuni pe mai multe niveluri, aceste sisteme gestionează în mod inteligent procesarea simultană a mai multor instrucțiuni.La rândul său, acestea minimizează timpul de oprire a procesorului și ridică debitul general.Prioritizarea comenzilor simple, frecvent utilizate, alături de paradigma de încărcare și stocare care limitează interacțiunile de memorie, are ca rezultat utilizarea optimizată a registrului.În mediile de zi cu zi, unde execuția rapidă vă poate afecta semnificativ experiența și satisfacția, aceste strategii strălucesc.

Navigarea provocărilor de viteză cu tehnici sofisticate de execuție

Pentru a aborda barierele potențiale ale vitezei de la discrepanțele de ramificare și viteză de memorie, sistemele RISC folosesc în mod inteligent execuția speculativă și procesarea în afara ordinului.Aceste strategii împuternicesc procesorul să anticipeze și să se pregătească pentru o varietate de căi de instrucțiuni, asigurând în cele din urmă o execuție lină în situații complexe.Înțelegerea acestor metodologii oferă o perspectivă profundă asupra principiilor de optimizare care modelează proiectele de procesor de ultimă oră de azi, reflectând subtil călătoria unei industrii către soluții de calcul mai inteligente și mai intuitive.

Ridicarea lățimii de bandă cu arhitecturi strategice de cache

Îmbunătățirile arhitecturii cache joacă un rol în creșterea lățimii de bandă, facilitarea furnizării de instrucțiuni eficiente și fluide către CPU.Aceste strategii reduc cu adept latența, permițând accesul rapid la datele utilizate frecvent, o necesitate pentru procesarea rapidă în aplicații diverse.În acțiune, astfel de metodologii duc la o reacție și performanță îmbunătățită a sistemului, satisfăcând cerințele industriilor în care calculul de înaltă performanță este mai mult decât o simplă comoditate.

Dinamica performanței comparative cu proiectele CISC

Prin aceste metodologii avansate, procesoarele RISC de la companii precum Intel, AMD și Cyrix obțin valori de performanță care le eclipsează pe cele ale proiectelor tradiționale CISC.Această margine de performanță marcată este observată în gestionarea pricepută a RISC a sarcinilor complexe, ceea ce face ca aceste procesoare să fie o alegere de top în sectoarele în care se dorește puterea de procesare formidabilă.Aceste perspective se aliniază cu schimbări tehnologice mai largi și arată o imprimare neobosită pentru inovație, propulsând industria semiconductorilor către soluții de procesor scalabile care îndeplinesc setea în continuă evoluție de putere și eficiență.

Caracteristici ale arhitecturii RISC

Set de instrucțiuni eficient

Arhitectura RISC se învârte în jurul setului său de instrucțiuni minime, cu mai puțin de 128 de instrucțiuni.Aceste instrucțiuni sunt definite prin modurile lor de adresare clare și formatul consistent.Prin determinarea accentului către reducere, sistemele RISC îmbunătățesc în mod activ viteza cu tehnici precum conducta de instrucțiuni și o abordare de încărcare/magazin, permițând sarcinilor să se termine într -un singur ciclu de mașină.Această abordare simplă nu numai că accelerează executarea sarcinilor, dar facilitează și un proces de decodare a instrucțiunilor adept, satisfacerea cerințelor moderne de calcul care apar pentru eficiență și viteză.

Control direct pentru o execuție îmbunătățită

În arhitecturile RISC, mecanismele de control cu fir greu au adesea prioritate asupra microprogramărilor.Această alegere simplifică proiectarea procesorului și accentuează operațiunile rapide și fiabile.Prin ocolirea etapelor de control intermediar, procesoarele funcționează într -o manieră mai directă și mai eficientă, un nod la nerăbdarea cu întârzieri și dorință de imediatitate.Această metodologie permite o concentrare mai accentuată pe rafinarea proceselor și obținerea performanței ridicate, demonstrând impactul practic al reducerii latenței deciziei asupra capacităților sistemului.

Depozitare extinsă a registrului și gestionarea datelor

Băncile de înregistrare abundente în sistemele RISC consolidează eficiența de gestionare a datelor.Reduce accesul frecvent al memoriei, servind ca stocare cu acces rapid și atenuând încetinirea cauzată de întârzierile de memorie.Capacitățile de stocare a registrului mai mari facilitează procesarea mai mare a datelor, îmbunătățind viteza generală a sistemului.Această concentrare pe gestionarea internă a datelor rezonează cu proclivitatea către o execuție perfectă și fără probleme, subliniind angajamentul RISC față de un randament ridicat de procesare, păstrând în același timp o complexitate rafinată a hardware-ului.

Accentul pe procesarea priceperii

Opțiunile strategice de proiectare încorporate în RISC sunt elaborate pentru a maximiza eficiența, păstrând complexitatea hardware scăzută.Acest lucru reflectă nu doar o ambiție teoretică, ci o observație pragmatică în multe aplicații, unde operațiunile simplificate produc experiențe de calcul rapid receptive.Prin prioritate debitului și simplității, Risc orchestrează în mod inteligent resurse de calcul pentru a aborda procesele sofisticate cu poise.Această intenție consolidează rolul RISC în calculul modern și influențează traiectoriile de dezvoltare a procesorului, validând marginea arhitecturală oferită de seturi de instrucțiuni compacte în realizarea unei performanțe impresionante cu design mindful.

Avantajul arhitecturii RISC

Proiectare și integrare simplificată

Arhitectura RISC se remarcă cu avantajele sale distincte, în special compatibilitatea sa cu tehnologia de integrare la scară largă (VLSI).Proiectarea sa simplă duce la dimensiunile reduse ale cipurilor și la o fiabilitate sporită prin minimizarea erorilor de proiectare.În proiectarea procesorului, optarea pentru o abordare mai puțin complicată are ca rezultat adesea o producție mai eficientă și o calendar mai scurtă de dezvoltare.Acest principiu se aliniază cu ideile care prețuiesc eliminând complexitățile inutile pentru a obține funcționalitatea maximă.

Viteză crescută și eficacitate din punct de vedere al costurilor

Unitățile de control eficiente din cadrul procesoarelor RISC promovează viteze de procesare mai rapide, alături de cheltuieli de proiectare reduse.Această metodologie oferă căi clare și directe pentru executarea instrucțiunilor, contribuind la utilizarea eficientă a energiei și la o productivitate operațională ridicată.Astfel de îmbunătățiri ale prelucrării vitezei și conservării energiei se armonizează perfect cu nevoile industriei pentru soluții eficiente din punct de vedere al costurilor, oferind un avantaj tactic în inovația hardware.

Compatibilitatea cu limbile la nivel înalt

Strategia de proiectare a RISC susține limbaje de programare la nivel înalt, mai degrabă decât limbaje de asamblare, în concordanță cu tendințele de dezvoltare contemporane.Se adresează eficient provocării persistente cunoscute sub numele de „criza software”.Această aliniere simplifică depanarea și întreținerea, creând un mediu care promovează inovația și prototiparea rapidă, fără limitările programării la nivel scăzut.Mulți dezvoltatori de software apreciază rezultatele de performanță fiabile pe care RISC Architecture le oferă, care le simplifică eforturile, sporind eficiența.

Integrarea software și optimizarea simplificată

Un factor de succes al arhitecturii RISC este integrarea sa perfectă cu sistemele software existente, facilitate prin procese de recompilare care se stresează compatibilitatea.Această caracteristică îmbunătățește foarte mult experiența prin furnizarea de programatori un set de instrucțiuni consistente care simplifică optimizarea codului și predictibilitatea.Profesioniștii din industria software apreciază claritatea și uniformitatea pe care o aduce la procesul de dezvoltare, reducând neconcordanțele între diverse configurații hardware și software.

Provocări și orizonturi viitoare

Complexități intrinseci

Arhitectura RISC, lăudată pentru designul său eficient și simplu, se confruntă cu complexități inerente.O problemă semnificativă este cererea crescută de memorie datorită lungimii instrucțiunilor compilate, care poate stârni anxietatea asupra capacității de stocare și a recuperării datelor.Prezența unor seturi de registre ample se adaugă sarcinii prin complicarea schemelor de adresare, cerând soluții atentă.Limitele de instrucțiuni cu un singur cuvânt introduc provocări atunci când se gestionează spațiul de adrese pe 32 de biți, necesitând adesea instrucțiuni cu două cuvinte pentru gestionarea eficientă a datelor.Realizarea unui echilibru între utilizarea eficientă a memoriei și apelurile optime de performanță pentru rezolvarea creativă a problemelor și ajustări precise.

Evoluție și armonizare

În ciuda acestor provocări înnăscute, potențialul RISC este fortificat de capacitatea sa de a se adapta și de a evolua.Amestecul continuu de elemente RISC și CISC indică un model hibrid care utilizează tot ce este mai bun din ambele lumi, ceea ce indică o relație de cooperare mai degrabă decât una competitivă.În special, apariția arhitecturilor Superscalar și superpipeline joacă un rol, deoarece acestea îmbunătățesc foarte mult performanța RISC.Aceste progrese stimulează capacitățile procesorului, permițând procesarea mai multor instrucțiuni simultan în timpul fiecărui ciclu, o capacitate care găsește extrem de avantajoasă în medii cu cerințe de calcul intensive.

Influență susținută asupra peisajului tehnologic

Creșterea adaptabilă a RISC asigură semnificația și influența continuă în conturarea viitoarelor procesoare și domeniul expansiv al calculului.Pe măsură ce cerințele privind puterea de calcul și eficiența cresc, RISC este gata să conducă progresul tehnologic.Eficiențele sale înnăscute oferă o valoare susținută în diverse aplicații, de la sisteme încorporate la soluții de calcul de înaltă calitate.Utilizarea practică a RISC în sisteme evidențiază rolul său în scenarii în care este important momentul de execuție previzibil.În consecință, RISC continuă să servească nu doar ca o tehnologie de bază, ci ca o componentă excelentă care inspiră următorul val de inovații în arhitectura de calcul.

Perspectivele tehnologiei RISC

RISC (computer de setare de instrucțiuni reduse) se concentrează pe simplificarea proiectării procesorului pentru a accelera execuția instrucțiunilor, contrastând cu CISC (computer de instrucțiuni complexe), care prioritizează ușurința de programare prin instrucțiuni mai complexe.Procesoarele moderne îmbină adesea ambele abordări pentru a obține performanțe mai bune.De exemplu, jetoane precum 80486 de la Intel și Motorola 68040 încorporează tehnici RISC pentru a reduce timpii de instrucțiuni la sub 2 cicluri, în timp ce Fairchild Clipper atinge viteze de până la 33 MIP -uri prin combinarea elementelor RISC și CISC.Noile progrese, cum ar fi SuperScalar și Superpipelining Technologies, împing performanța RISC în continuare, permițând procesarea simultană a instrucțiunilor multiple.Procesoare precum RS/6000 de la IBM pot executa până la șase instrucțiuni pe ciclu folosind aceste metode.Cu toate acestea, alții prezic că câștigurile viitoare se vor concentra mai puțin pe viteza brută și mai mult pe îmbunătățirea eficienței cache -ului, a compilatorilor și a sistemelor multiprocesorului.

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

Ghid cuprinzător pentru bancile de testare: Instrumente și tehnici pentru verificarea sistemului digital

pe 2025/01/7

Un ghid cuprinzător pentru osciloscopuri pentru analiza semnalului

pe 2025/01/7

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/18 147749

-

Pinut și caracteristici USB-C

pe 2000/04/18 111921

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/18 111349

-

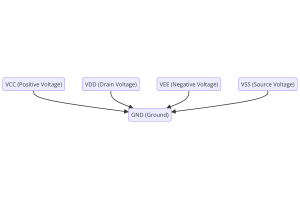

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/18 83714

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79502

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66872

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63005

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 62954

-

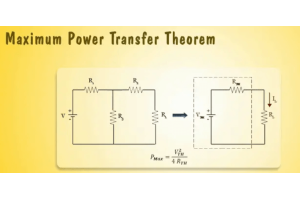

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54078

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52092