XCV200-6FG456C FPGA: Caracteristici, specificații, programare și aplicații

XCV200-6FG456C este un FPGA puternic (tablou de poartă programabil pe câmp) din seria AMD Xilinx Virtex®.Acest ghid explică caracteristicile sale, aspectul pinului, pașii de programare și utilizările.Cu o putere de procesare ridicată, opțiuni de proiectare flexibile și capacități puternice de intrare/ieșire (I/O), acest FPGA ajută la construirea sistemelor digitale rapide și fiabile.Indiferent dacă lucrați la rețele, sisteme de control sau electronice personalizate, acest ghid vă va ajuta să înțelegeți cum poate fi utilizat XCV200-6FG456C în proiectele dvs.Catalog

Prezentare generală XCV200-6FG456C

XCV200-6FG456C este un model notabil în cadrul familiei AMD Xilinx Virtex® FPGA, conceput pentru a oferi soluții logice programabile robuste pentru sisteme digitale complexe.Acest cip specific cuprinde aproximativ 236.666 de porți ale sistemului și dispune de 1.176 blocuri logice configurabile (CLBS) și 5.292 celule logice.De asemenea, include 57.344 biți de ram totale și acceptă 284 pini de I/O, adăpostiți într-un pachet de grilă cu bilă cu bilă fină de 456 cu bilă (FBGA), care măsoară 23mm x 23mm.Acest model funcționează pe o tensiune nominală de 2,5V, cu un interval de 2,375V la 2.625V și poate funcționa într -un interval de temperatură de la 0 ° C la 85 ° C.Seria Virtex® mai largă se referă la o serie de aplicații cu densități de la 50.000 la peste 1 milion de porți ale sistemului și rate de ceas ale sistemului de până la 200 MHz.Suportă numeroase standarde I/O, inclusiv LVTTL, LVCMOS și PCI, printre altele.Caracteristici precum bucle blocate cu întârziere (DLLS), blocuri logice configurabile cu memorie încorporată și logică dedicată de transport pentru operațiuni aritmetice își îmbunătățesc funcționalitatea.Fabricat folosind un proces de metal cu 5 straturi de 0,22 um, familia Virtex® garantează performanța și fiabilitatea.

Dacă doriți să integrați tehnologia FPGA de top în produsele sau sistemele dvs., cumpărarea XCV200-6FG456C în vrac cu noi este o mișcare inteligentă.Acesta respectă standardele industriei și vă menține înaintea nevoilor viitoare de tehnologie.

Caracteristici XCV200-6FG456C

• Porți de sistem: XCV200-6FG456C oferă aproximativ 236.666 de porți ale sistemului.Acest număr de poartă înaltă permite implementarea circuitelor logice digitale integrate complexe pe un singur cip, sporind atât performanța, cât și versatilitatea într -o gamă de aplicații.

• Resurse logice: Include 1.176 blocuri logice configurabile (CLB) și 5.292 celule logice.Aceste resurse sunt bune pentru proiectarea circuitelor digitale flexibile și scalabile.CLB -urile pot fi programate pentru a efectua o mare varietate de funcții logice, în timp ce numărul mare de celule logice permite gestionarea operațiunilor și proceselor logice extinse.

• Memorie: Dispozitivul oferă 57.344 de biți de memorie RAM, distribuite între blocurile sale logice.Acest RAM încorporat este utilizat pentru aplicații care necesită stocare și regăsire rapidă și eficientă a datelor, sprijinind operațiuni de date de mare viteză integrale sistemelor digitale moderne.

• Capabilități I/O.: Cu 284 pini de intrare/ieșire, XCV200-6FG456C facilitează capacități extinse de interfață.Acești pini de I/O acceptă diverse standarde de semnal și permit FPGA să comunice eficient cu alte componente dintr -un sistem, cum ar fi dispozitive de memorie, procesoare și periferice.

• Tensiune și interval de temperatură: Funcționând la o tensiune nominală de 2,5V, cu un interval acceptabil de la 2.375V la 2.625V, acest FPGA este proiectat pentru un consum redus de putere, menținând în același timp o performanță robustă.Poate funcționa într -un interval de temperatură al joncțiunii de la 0 ° C la 85 ° C, asigurând fiabilitatea în diferite condiții de mediu.

XCV200-6FG456C Diagrama funcției pinului

XCV200-6FG456C Diagrama funcției pinului este o reprezentare structurată a misiunilor PIN ale FPGA, clasificate în diferite bănci (Banca 0 la bancă 7)Fiecare grup de grupuri bancare se bazează pe funcția și plasarea fizică pe pachetul FPGA.Sistemul de numerotare și etichetare urmează un model de grilă în care rândurile sunt notate prin litere (A, B, C, etc.) și coloane după numere (1, 2, 3 etc.), care facilitează identificarea rapidă a pinilor specifici.Aceste bănci corespund diferitelor funcții de intrare/ieșire, putere, sol și rutare dedicată semnalului.Pinii li se atribuie diverse grupări funcționale, inclusiv I/O (GPIO) cu scop general, adesea etichetate drept „G” (intrare/ieșire generală), „V” (alimentare de tensiune) și „O” (ieșire).Pinii de putere și sol sunt marcați în mod distinct, asigurând o funcționare stabilă a FPGA.Pinii cu scop special, cum ar fi intrările de ceas, resetările și semnalele de control sunt identificate cu simboluri precum „R” sau „T.”Unele pini servesc, de asemenea, roluri de comunicare dedicate, inclusiv configurația JTAG și ceasul de mare viteză, pentru programare și depanare.

XCV200-6FG456C Diagrama blocului

Bloc de intrare/ieșire

Diagrama reprezintă Bloc de intrare/ieșire (IOB) Structura FPGA XCV200-6FG456C, care este un membru al familiei Xilinx Virtex.Diagrama prezintă elemente cheie implicate în operațiunile de intrare și ieșire, subliniind mecanismele de flux de date și de control.În centrul diagramei, trei flip-flop-uri D sunt utilizate pentru a înregistra semnale pentru controlul de intrare, ieșire și tri-stat.Registrul de ieșire este controlat de semnalul OCE (Activare ceas de ieșire), care determină când datele de ieșire sunt fixate.În mod similar, registrul tri-stat este controlat de TCE (Tri-State Clock Enable), care permite sau dezactivează tamponul de ieșire.Registrul de intrare surprinde datele primite și aplică o întârziere programabilă înainte de a le trece la logica FPGA internă prin intermediul IBUF (buffer de intrare).OBUFT (tampon de ieșire Tri-State) asigură că FPGA poate conduce un semnal pe PAD (PIN I/O) sau să îl plaseze într-o stare de impedanță mare, în funcție de logica de control.Pe plajă este inclus un circuit slab de păstrător pentru a menține ultima stare logică cunoscută atunci când nu este prezent un șofer activ, împiedicând condițiile plutitoare neintenționate.Tensiunea de referință (VREF) este utilizată pentru anumite standarde de intrare, cum ar fi SSTL sau HSTL, care necesită niveluri de tensiune precise pentru o funcționare corectă.În general, această structură IOB permite FPGA să gestioneze transmisia de date de mare viteză, să suporte diferite standarde de I/O și să ofere un control flexibil asupra calendarului și integrității semnalului.

Mod de serie Master/Slave

Mod de serie Master/Slave Block Diagram ilustrează procesul de configurare al unui Virtex FPGA, în special XCV200-6FG456C, atunci când este programat într-o configurație a lanțului de margarete folosind un EEPROM serial (XC1701L).În această configurație, un dispozitiv Virtex funcționează ca master, controlând ceasul de configurare (CCLK) și transmiterea serială a datelor de configurare către FPGA -uri suplimentare sclave din lanț.Master FPGA inițiază procesul de configurare afirmând semnalul programului, resetarea tuturor dispozitivelor din lanț.Odată ce inițializarea este completă, semnalul INIT indică pregătirea, iar datele de configurare fluxuri de la EEPROM serial (XC1701L) până la pinul DIN (date în) al FPGA principal.Master FPGA citește datele de la EEPROM și le transmite prin Dout (date out) către FPGA -urile sclave ulterioare, sincronizând transferul de date folosind semnalul CCLK.Semnalul Done este utilizat pentru a indica o configurație de succes, cu o rezistență opțională de tracțiune asigurând o stare stabilă înaltă atunci când configurația este completă.XC1701L EEPROM este controlat de FPGA Master folosind semnale CLK, Date, CE (CHIP) și Reset/OE (Enable Output), asigurându -se că datele de configurare stocate sunt preluate corect.Această metodă de configurare este eficientă pentru programarea mai multor FPGAs folosind un singur EEPROM, reducând complexitatea de cablare externă și asigurând că toate dispozitivele primesc date de configurare sincronizate.

Specificații XCV200-6FG456C

|

Tip |

Parametru |

|

Producător |

Amd xilinx

|

|

Serie |

Virtex® |

|

Ambalaj |

Tavă |

|

Starea părții |

Învechit |

|

Numărul de laboratoare/CLBS |

1176 |

|

Numărul de elemente/celule logice |

5292 |

|

Biți de ram totale |

57344 |

|

Numărul de I/O. |

284 |

|

Numărul de porți |

236666 |

|

Tensiune - alimentare |

2.375V ~ 2.625V |

|

Tip de montare |

Montare la suprafață |

|

Temperatura de funcționare |

0 ° C ~ 85 ° C (TJ) |

|

Pachet / carcasă |

456-BBGA |

|

Pachet de dispozitive furnizor |

456-FBGA (23x23) |

|

Numărul produsului de bază |

XCV200 |

Aplicații XCV200-6FG456C

Telecomunicații și rețele

XCV200-6FG456C excelează în aplicațiile de telecomunicații și de rețea datorită capacității sale de a gestiona transmisii de date de mare viteză și sarcini complexe de procesare a semnalului.Numărul său înalt de poartă și capacitățile de I/O robuste îi permit să suporte funcții precum procesarea pachetelor, modularea semnalului/demodularea și protocoalele de corecție a erorilor.

Prelucrarea digitală a semnalului (DSP)

Ideal pentru aplicațiile DSP, acest FPGA poate efectua calcule matematice rapide și complexe necesare în tehnologiile de procesare audio și video.Fie că este vorba de sisteme multimedia, de recunoaștere vocală sau de servicii de streaming, capacitățile puternice de procesare XCV200-6FG456C și memoria încorporată acceptă procesarea semnalului eficient și de înaltă calitate.

Sisteme de control industrial

În automatizarea industrială, XCV200-6FG456C oferă performanțele necesare pentru gestionarea sistemelor de control și a rețelelor de automatizare.Capacitatea sa de a executa mai multe sarcini de control simultan, asigurând în același timp timpii de răspuns o face potrivită pentru aplicațiile în controlul proceselor, robotica și viziunea mașinii.

Instrumente medicale

Precizia și viteza FPGA sunt excelente în imagistica medicală și în echipamentele de diagnosticare, unde ajută la procesarea algoritmilor complexi pentru aplicații imagistice, cum ar fi RMN, ultrasunete și scanări CT.Capacitățile XCV200-6FG456C se asigură că poate gestiona un randament ridicat de date și procesarea complexă necesară în tehnologia medicală modernă.

XCV200-6FG456C Piese similare

Pași de programare XCV200-6FG456C

Pași de programare pentru XCV200-6FG456C:

1. Intrare de proiectare

Faza inițială a programării FPGA implică definirea logicii digitale și a funcționalității sistemului dvs.Acest lucru se poate face folosind limbi de descriere hardware (HDL), cum ar fi VHDL sau Verilog, unde scrieți cod care specifică modul în care FPGA procesează datele și interacționează cu alte hardware.Instrumentele de intrare schematice disponibile în software -ul de proiectare FPGA precum Xilinx ISE sau Vivado pot fi utilizate.Această metodă implică crearea unei reprezentări vizuale a logicii prin glisarea și aruncarea componentelor, pe care unii le găsesc mai intuitiv decât scrierea codului.

2. Sinteză

După finalizarea proiectării, următorul pas este sinteza, în care un instrument precum XST -ul XST (XILINX Synthesis Technology) transformă codul HDL sau designul schematic într -o listă net.Acest Netlist descrie circuitul în termeni de componente digitale generice, cum ar fi porțile și registrele logice.Procesul de sinteză implică, de asemenea, optimizarea proiectării pentru a îndeplini cerințele de performanță și minimizarea utilizării resurselor pentru o funcționare eficientă a FPGA.

3. Implementare

Procesul de implementare începe cu traducerea, combinând designul dvs. cu fișiere de constrângere care specifică parametri, cum ar fi frecvențele de ceas și alocările PIN.În urma traducerii, etapa de mapare atribuie elementele listei de net la resurse fizice specifice de pe FPGA, cum ar fi tabele de căutare (LUTS) și flip-flops.Faza de plasare și rutare determină apoi locațiile fizice ale fiecărei componente din arhitectura FPGA și stabilește conexiunile dintre ele prin resurse de interconectare programabile.Această etapă este excelentă pentru realizarea valorilor de performanță dorite, inclusiv frecvențele ceasului.

4. Generația bitstream

După plasarea și rutarea cu succes, instrumentul generează un bitstream, un fișier de configurare binară care conține toate informațiile de programare pentru FPGA.De multe ori este recomandat să se simuleze designul final post-plasare pentru a se asigura că bitstream-ul se va comporta așa cum era de așteptat în condiții.Această etapă de verificare ajută la evitarea problemelor potențiale în timpul funcționării efective.

5. Configurare

Ultima etapă implică încărcarea bitstream -ului în FPGA folosind diverse metode de configurare.Modul Slave-Serial, o opțiune simplă și rentabilă, configurează FPGA printr-un dispozitiv principal extern care trimite date în serie.În modul master-serial, FPGA citește în mod autonom bitstream-ul dintr-un bal serial atașat.Pentru configurații de mare viteză, modul SelectMap permite unui microprocesor extern să încarce rapid datele în FPGA.În plus, modul JTAG este utilizat nu numai pentru programare, ci și pentru testare și depanare, utilizând o interfață standard pentru programarea în sistem și testarea scanii de graniță.

XCV200-6FG456C Avantaje

Performanţă

Seria Xilinx Virtex, din care face parte XCV200-6FG456C, este optimizat pentru performanță de mare viteză, oferind rate de ceas ale sistemului de până la 200 MHz.Acest lucru îl face bine potrivit pentru aplicațiile care necesită o prelucrare rapidă a datelor, asigurând o gestionare eficientă a algoritmilor complexi și a operațiunilor de mare viteză, cum ar fi telecomunicații, procesare și multimedia.

Standarde I/O Suport

Acest FPGA acceptă o gamă largă de standarde de intrare/ieșire, inclusiv LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT și AGP.Un astfel de suport extins de standarde I/O permite XCV200-6FG456C să se integreze perfect cu diverse componente ale sistemului, îmbunătățindu-și utilitatea pe diverse ecosisteme digitale.Această flexibilitate permite adaptarea FPGA la diferite condiții de interfațare fără modificări ale sistemului.

Gestionarea ceasului

XCV200-6FG456C încorporează mai multe bucle blocate cu întârziere (DLLS) pentru distribuirea și gestionarea ceasului în sistem.Aceste DLL -uri ajută la îmbunătățirea calendarului și fiabilității sistemului, oferind semnale de ceas precise necesare pentru operațiuni sincrone.Această caracteristică este importantă în reducerea erorilor sistemului și în îmbunătățirea performanței generale, în special în proiectele complexe care necesită sincronizare și sincronizare exactă.

Flexibilitatea proiectării

Cu 1.176 de blocuri logice configurabile și 5.292 de celule logice, XCV200-6FG456C oferă resurse logice substanțiale, cu capacitatea de a implementa o gamă diversă de funcționalități.De la logică simplă de lipici la sisteme digitale complexe, acest FPGA acceptă cerințe complexe de proiectare, ceea ce o face ideală pentru aplicații în calculul personalizat, procesarea digitală a semnalului și prototiparea.

Prototiparea rapidă

FPGA precum XCV200-6FG456C sunt renumite pentru capacitatea lor de a sprijini prototiparea rapidă.Acest dispozitiv permite iterații de proiectare rapidă și poate fi reconfigurat pe teren, ceea ce reprezintă un avantaj pentru ciclurile de dezvoltare, deoarece reduce timpul la piață.De asemenea, se adaptează eficient la schimbarea cerințelor sau actualizărilor în specificațiile proiectului, asigurându-se că produsele finale sunt la zi cu cele mai recente standarde tehnologice.

Capacitate de integrare

Capacitățile de integrare ale XCV200-6FG456C facilitează consolidarea mai multor componente discrete într-un singur cip.Această integrare poate duce la reducerea complexității sistemului, a consumului de energie mai mic și a economiilor de costuri.Prin minimizarea numărului de componente separate necesare, acest FPGA simplifică procesele de proiectare și îmbunătățește fiabilitatea și compactitatea sistemului general.

XCV200-6FG456C Dimensiuni de ambalare

XCV200-6FG456C este un tablou de poartă programabilă de câmp (FPGA) din seria Virtex® AMD, găzduit într-un pachet de grilă cu bilă fină de 456 cu bilă (FBGA).

• Tip de pachet: 456-FBGA

• Dimensiunea pachetului: 23 mm x 23 mm

• Pitch cu bilă: 1,0 mm

XCV200-6FG456C Producător

XCV200-6FG456C este un tablou de poartă programabilă de câmp (FPGA) dezvoltat inițial de Xilinx, o companie cunoscută pentru dispozitivele sale logice programabile de înaltă performanță.După achiziția lui Xilinx de către Amd, XCV200-6FG456C este acum asociat cu AMD ca producător actual.Cu toate acestea, acest model FPGA este învechit și nu mai este în producție.AMD continuă să sprijine arhitecturi FPGA mai noi, cu performanțe îmbunătățite, eficiență a puterii și longevitate extinsă, ceea ce face alternative moderne de preferat pentru noi modele.

Concluzie

XCV200-6FG456C este un FPGA versatil și de mare viteză, util pentru multe aplicații tehnologice.Deși nu mai este făcut, este totuși o alegere bună pentru sistemele mai vechi care au nevoie de performanțe fiabile.Acest ghid și -a acoperit proiectarea, pașii de programare și utilizările practice, ceea ce face mai ușor să înțeleagă cum funcționează și cum poate fi utilizat.Pe măsură ce FPGA -urile mai noi devin disponibile, puteți utiliza aceste cunoștințe pentru a alege FPGA potrivită pentru nevoile dvs. și pentru a îmbunătăți proiectele digitale.

Fișă de date pdf

Fișiere de date XCV200-6FG456C:

Despre noi

ALLELCO LIMITED

Citeste mai mult

Anchetă rapidă

Vă rugăm să trimiteți o întrebare, vom răspunde imediat.

întrebări frecvente [FAQ]

1. Care este consumul de energie al XCV200-6FG456C?

XCV200-6FG456C funcționează la 2,5V, cu un interval de tensiune de la 2.375V la 2.625V.Consumul de energie depinde de utilizarea logică și de frecvența ceasului, dar ca FPGA mai vechi, poate fi mai puțin eficient din punct de vedere al puterii decât dispozitivele Xilinx mai noi.Ar trebui luată în considerare gestionarea corectă a puterii și disiparea căldurii.

2. Cum se compară XCV200-6FG456C cu XCV200-6FG256C?

XCV200-6FG456C are un pachet mai mare (FBGA cu 456-ball) comparativ cu XCV200-6FG256C (256-Ball FBGA), oferind mai mulți pini I/O (284 vs. 172) și performanțe potențial mai bune pentru aplicații care necesită o interfață extinsă.Dacă designul dvs. se bazează pe mai multe capacități de I/O, XCV200-6FG456C este alegerea mai bună.

3. Pot reprograma XCV200-6FG456C de mai multe ori?

Da, XCV200-6FG456C este un FPGA bazat pe SRAM, ceea ce înseamnă că poate fi reprogramat de un număr nelimitat de ori, atâta timp cât este furnizată puterea.Cu toate acestea, veți avea nevoie de memorie externă non-volatilă (EEPROM sau Flash) pentru a păstra bitstream-ul după un ciclu de putere.

4.. XCV200-6FG456C acceptă comunicarea în serie de mare viteză?

XCV200-6FG456C acceptă mai multe standarde de I/O precum LVTTL, LVCMOS, PCI, GTL, HSTL și SSTL, dar nu are serde de mare viteză încorporate (serializator/deserializator) sau transceiver precum FPGA moderne.Pentru aplicațiile care necesită legături seriale de mare viteză (de exemplu, PCIe, Gigabit Ethernet sau HDMI), luați în considerare modele FPGA mai noi.

5. Cum se compară XCV200-6FG456C cu modelele FPGA mai noi?

XCV200-6FG456C aparține unei generații mai vechi de FPGA.În comparație cu FPGA -urile moderne Virtex, are un număr mai mic de poartă, viteze mai lente ale ceasului și o eficiență limitată a puterii.Modelele mai noi oferă o densitate logică mai mare, o memorie mai încorporată, blocuri DSP avansate și un consum de energie mai mic, ceea ce le face mai bune pentru aplicațiile moderne.

AD73322AR PINOUT, Caracteristici și detalii tehnice explicate

pe 2025/03/21

EP20K100EFC324-1X FPGA: Caracteristici, specificații, aplicații și Ghid de programare

pe 2025/03/20

Postări populare

-

Set de instrucțiuni complexe Calculatoare: Cum au schimbat calculul?

pe 8000/04/19 147782

-

Pinut și caracteristici USB-C

pe 2000/04/19 112064

-

Utilizarea Primitivelor de simulare unificată Xilinx: un ghid cuprinzător pentru proiectarea și simularea FPGA

pe 1600/04/19 111352

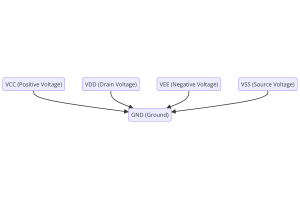

-

Tensiunile sursei de alimentare în electronică: semnificația VCC, VDD, VEE, VSS și GND

pe 0400/04/19 83819

-

Ghidul conectorului RJ45: PINOUT, cabluri, tipuri de cablu și utilizări

pe 1970/01/1 79639

-

Ghidul final pentru codurile de culori de sârmă în sistemele electrice moderne

Modul în care sistemele noastre electrice folosesc culorile nu este doar pentru aspect.Fiecare culoare de sârmă indică acum o funcție specifică, ceea ce face mai ușor identificarea și gestionarea c...pe 1970/01/1 66999

-

Ghid de supapă de purjare: funcție, simptome, testare și înlocuire pentru performanța optimă a motorului

Supapa de purjare este o parte cheie a sistemului unei mașini care ajută la menținerea aerului curat prin gestionarea vaporii de combustibil înainte de a putea scăpa în atmosferă.Acest lucru nu num...pe 1970/01/1 63125

-

Factor de calitate (Q): ecuații și aplicații

Factorul de calitate, sau „Q”, este important atunci când verificați cât de bine lucrează inductorii și rezonatorii în sisteme electronice care utilizează frecvențe radio (RF).„Q” măsoară cât de bi...pe 1970/01/1 63062

-

Realizarea performanței maxime cu teorema maximă de transfer de putere

Teorema maximă de transfer de putere explică modul în care energia dintr -o sursă, cum ar fi o baterie sau un generator, curge la o sarcină conectată.Arată condiția exactă în care sarcina primește ...pe 1970/01/1 54097

-

Specificații și compatibilitate a bateriei A23

Bateria A23 este o baterie mică, în formă de cilindru, cu tensiune ridicată.De asemenea, numit 23A, 23AE sau MN21, se desfășoară la 12 volți și mult mai mare decât bateriile AA sau AAA.Des...pe 1970/01/1 52215